Hello, I would like to inquire about some technical details regarding the internal module power supply ranges, power-up sequences, and reset voltages for the nRF54L05, nRF54L15, nRF52805, and nRF52820:

-

The startup sequence during a power ramp-up (increasing voltage).

-

The voltage threshold that triggers a reset during a power ramp-down (decreasing voltage).

-

The time from when the core starts until Flash operations or access is available during the startup phase.

-

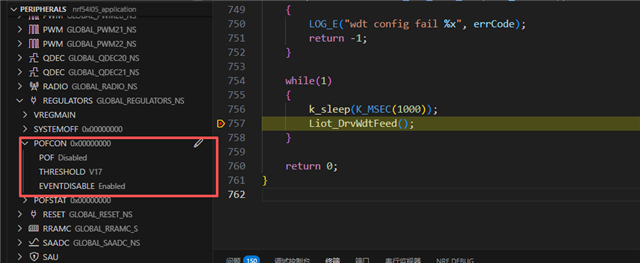

If the Power-Fail Comparator (POF) is configured, the time from when the core starts until the POF becomes effective during the startup phase.

It has been confirmed that there is no relevant information available on the one we inquired about. If the above-mentioned chips differ under these circumstances, please explain them separately.