On the previous nRF52833, the CPU cannot function normally during flash write or erase operations.

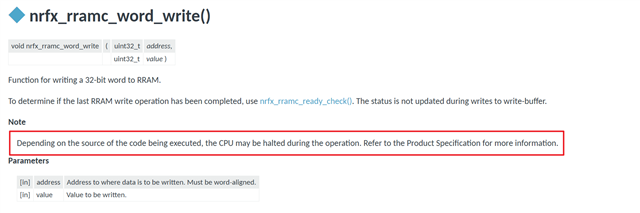

With the nRF54 series upgraded to RRAM, does a similar limitation still exist? Specifically, during RRAM read, write, or erase operations, can the CPU continue to run normally, and can interrupts be handled as expected?

I don't quite understand the statement that whether the CPU will halt depends on the source of the code. How should this be explained, and could you provide some examples?

Thanks!