Hi, Now I use the NRF51822 ADC to sample VCC , 1.2V internal reference,internal prescaling 1/3.The PCB connection show as the pictrue  .My application develop base on soft device-6.0 .The ADC starts to sample VCC when the application is waked up from

.My application develop base on soft device-6.0 .The ADC starts to sample VCC when the application is waked up from sd_app_evt_wait(). When connect the J-Link to debug the application,the ADC samples VCC correct ,once removing ,the ADC samples VCC voltage is higher 0.2V than the reality voltage,(eg. The VCC is 3.3V ,in debug model,ADC sample value is 3.29V,but in removing model, the result is 3.5V ).Is in the debug model the CPU running at full speed? I have tried testing the ADC works at CPU full running ,but the result is still wrong.

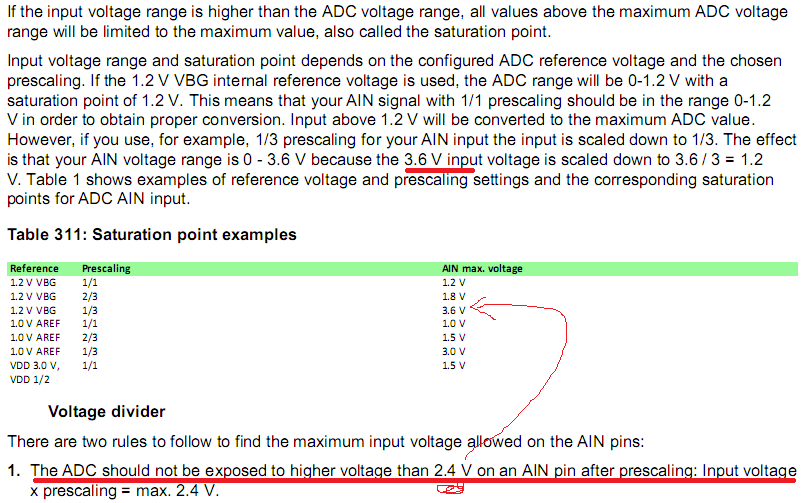

What does the picture mean?Is it saying that the AIN port voltage never can't be over 2.4V when using internal or external prescalling? By the way,use external crystal oscillator the accuracy is better than before,but the error still exsit,especially sampleing a high lever voltage(3.25V is sampled as 3.50V).

What does the picture mean?Is it saying that the AIN port voltage never can't be over 2.4V when using internal or external prescalling? By the way,use external crystal oscillator the accuracy is better than before,but the error still exsit,especially sampleing a high lever voltage(3.25V is sampled as 3.50V).