I'm just using nRF24LE1 to make 2.4G wireless mouse, mouse sensor is PAW3205DB-TJ3T. But i got a problem, PAW3205DB-TJ3T uses two-wire spi(SCKL+SDIO), nRF24LE1 only supports four-wire spi. So, what can i do?

---------update-------

I'm very grateful to you for your reply.I really want to give up.Because i have asked many people but nobody answer me.

This is the PAW3205DB Datasheet contains protocol and timing. link: pan.baidu.com/.../1kVIYrLP PWD: s7mp

I have try to use bit-bang the interface. But it has some problem. My code,read the ID to test communication is ok. RF_Mouse_PAW3205.zip

sometime,it will be ok when the mouse don`t move. I can read 0x30 at address 0x00, read 0xd1 at 0x01.

It will be fail when the mouse move. I try many times...

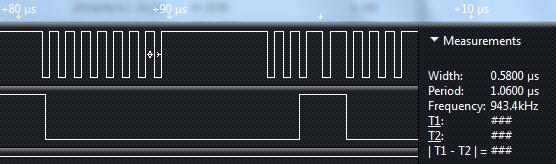

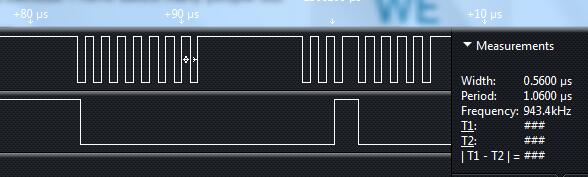

Detail logic: normal.logicdata abnormal.logicdata