Hello,

I am struggling with interfacing an I2S digital microphone to the nRF52. To be more concrete, it is the Knowles SPH0645LM4H-B. I connected it as suggested in this thread. In the data sheet of the microphone it says:

The SPH0645LM4H microphone operates as an I2S slave. The master must provide the BCLK and WS signals. The Over Sampling Rate is fixed at 64 therefore the WS signal must be BCLK/64 and synchronized to the BCLK. Clock frequencies from 2.048Mhz to 4.096MHz are supported so sampling rates from 32KHz to 64KHz can be had by changing the clock frequency. The Data Format is I2S, 24 bit, 2’s compliment, MSB first. The Data Precision is 18 bits, unused bits are zeros.

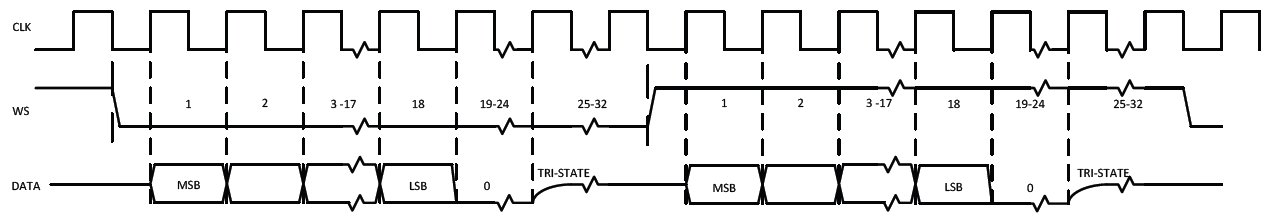

I find this contradictory with the figure also provided in the data sheet of the microphone:

In the image it is clear to see that WS toggles first after 32 clocks, which -for me- means, the word size is 32 bits (18 bits data, 6 bits set to 0, and 8 further bits floating).

The problem is that the nRF52's I2S interface does not support 32-bit word size.

/**

* @brief I2S sample widths.

*/

typedef enum

{

NRF_I2S_SWIDTH_8BIT = I2S_CONFIG_SWIDTH_SWIDTH_8Bit, ///< 8 bit.

NRF_I2S_SWIDTH_16BIT = I2S_CONFIG_SWIDTH_SWIDTH_16Bit, ///< 16 bit.

NRF_I2S_SWIDTH_24BIT = I2S_CONFIG_SWIDTH_SWIDTH_24Bit, ///< 24 bit.

} nrf_i2s_swidth_t;

No matter what settings I try with the available 8, 16, or 24 bit word-size, I can't get all the relevant data bits from the microphone's data stream.

Any ideas how to solve this problem? Or are these two components (nRF52 and Knowles mic) simply incompatible?

Thank you in advance! NewtoM