Hello,

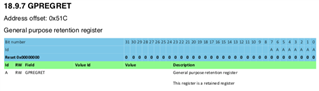

The Nordic documentation is pretty thin on what I can expect out of this 8-bit storage area. Perhaps some specific questions are in order:

-

How is it implemented? The fact that the sd_power_gpregret_clr() call specifies the bits to clear implies some form of flash.

-

Are the contents retained if I perform a bulk flash erase of the part?

-

Are the contents retained if I enter sd_power_system_off()?

-

the nRF51 Series Reference Manual states that its reset value is 0x00 - does that mean an external reset event over the SWD interface will clear it to zero?

-

Replies here suggest it is unavailable with the S210 SoftDevice. Is that still the case?

Thank you all very much and I apologize if these seem simplistic but I'd like to see all of this information in one area.

Dan Danknick