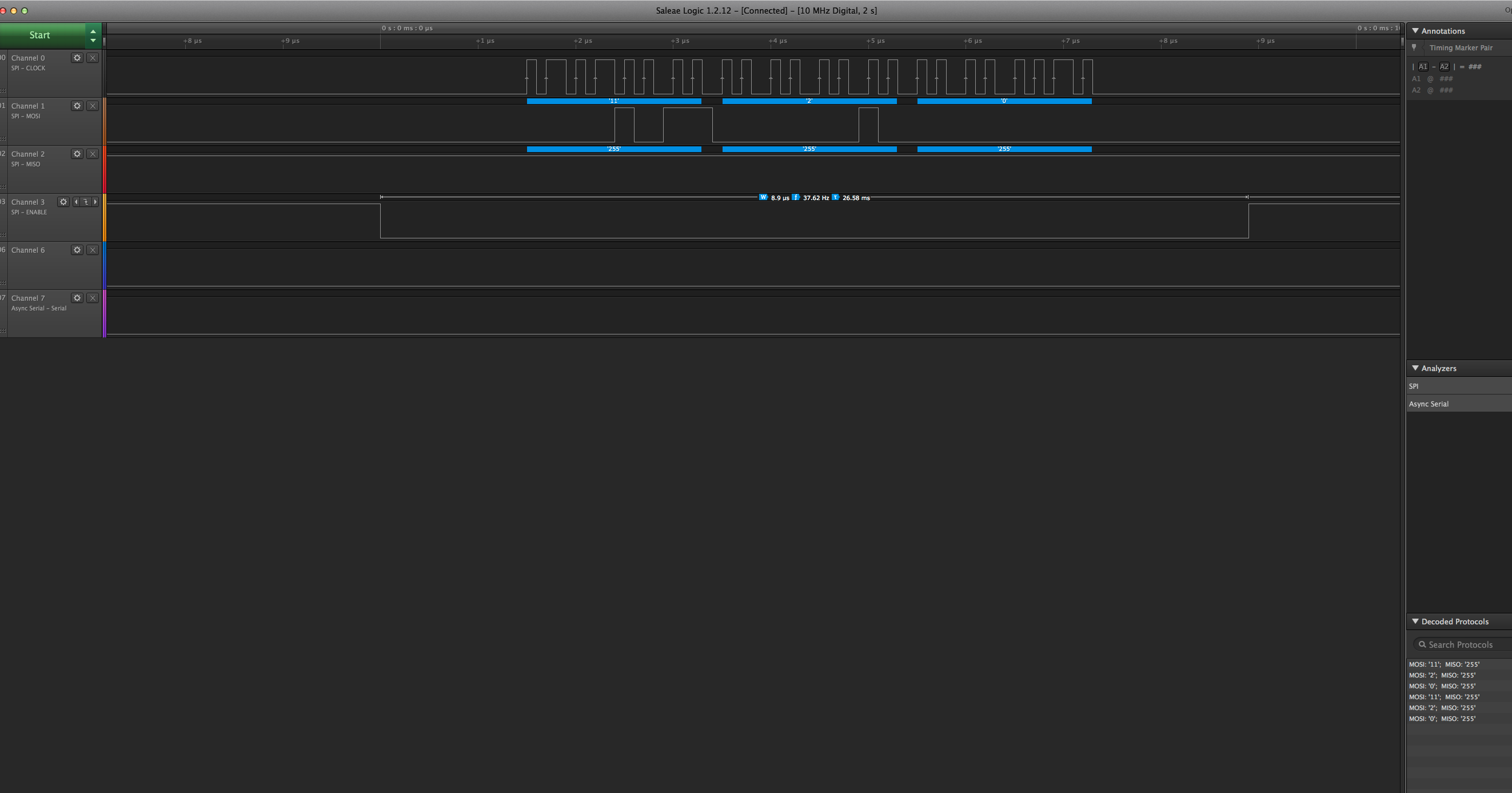

We have used a logic analyser to verify this.

SPI initialised and talks nicely with an ADXL362 accelerometer part.

We have interrupts configured.

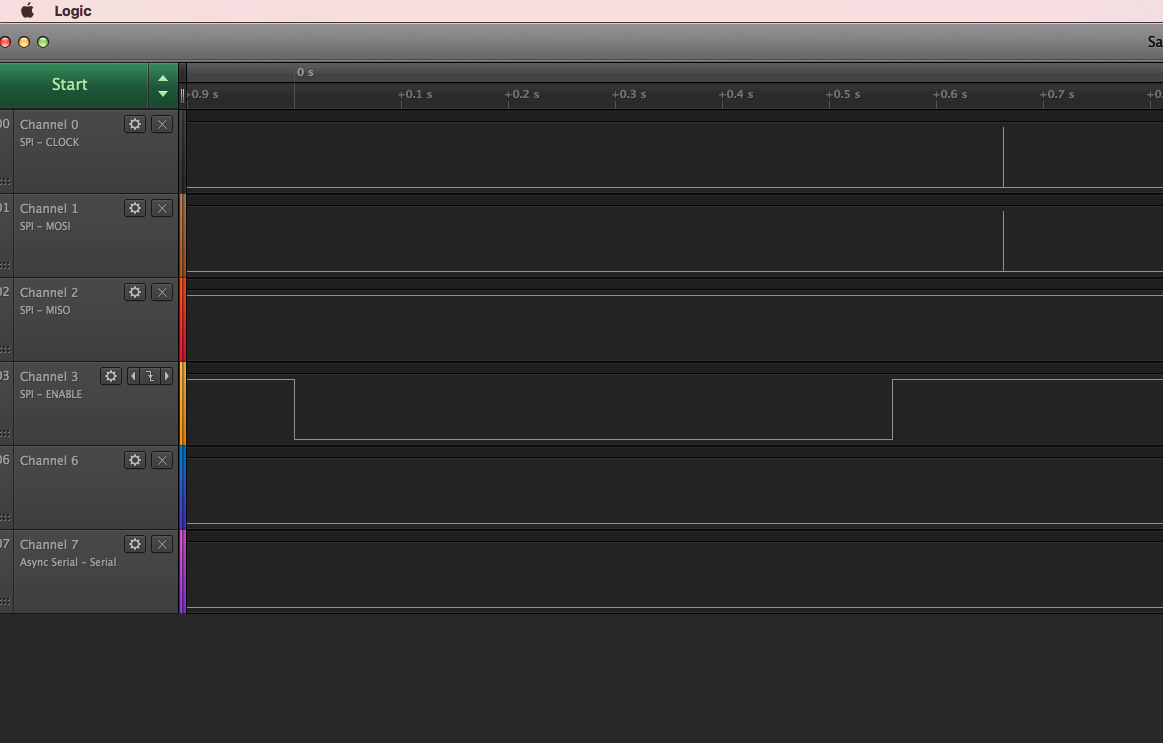

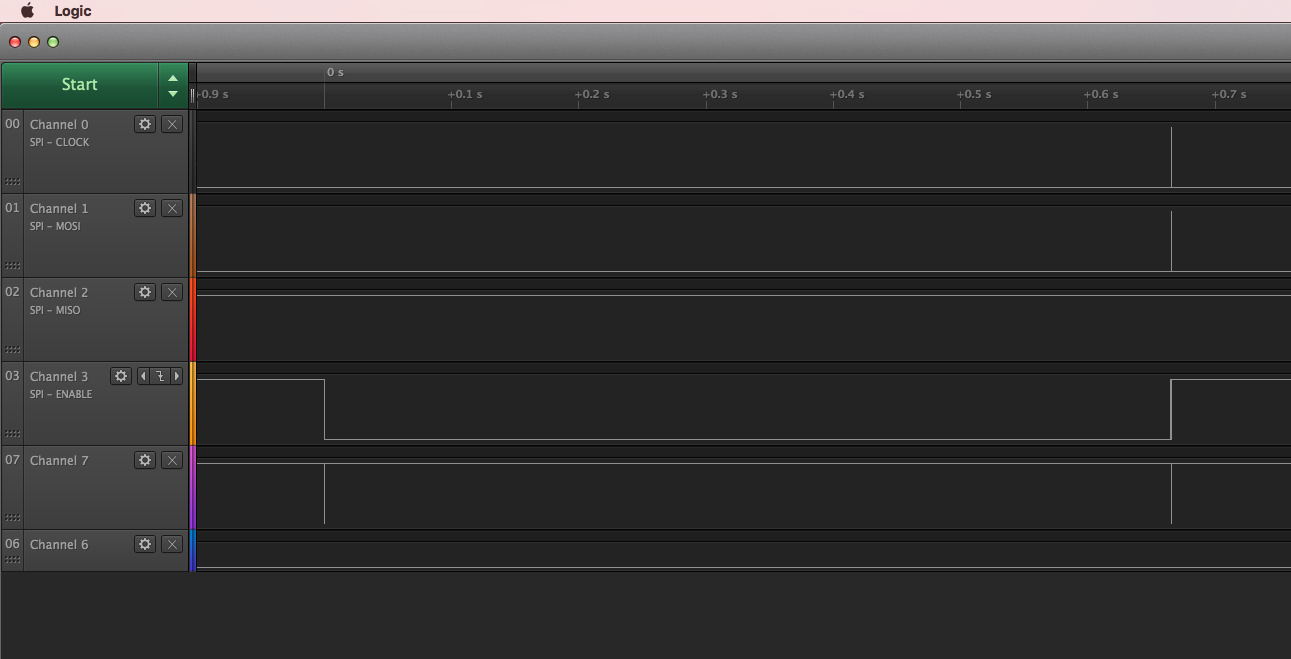

We go into sd_power_system_off()

Move board, interrupt fires, system wakes up (as no RAM retention or anything)

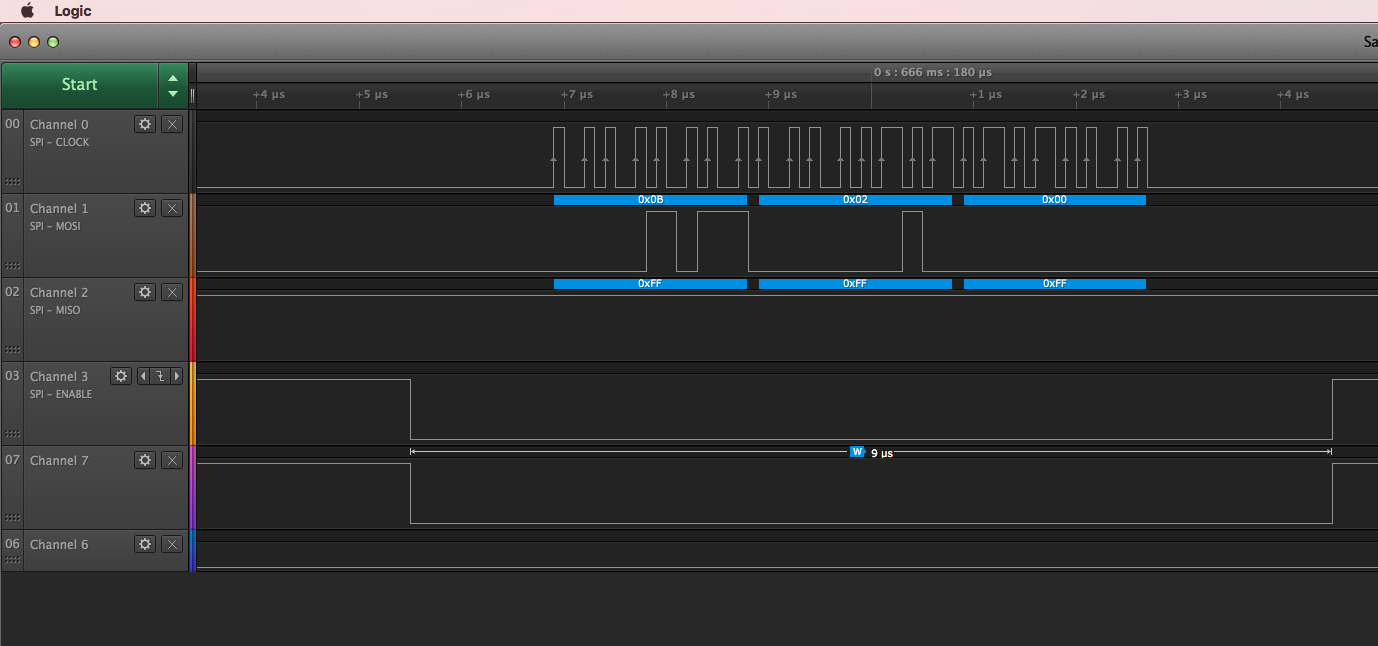

We re-init the SPI.

We attempt to chat over SPI to the ADXL362.

The Clock and the MOSI lines look exactly the same as before the reset (just reading an identity register)

The /CS line is stuck high.

Comparing the logic analyser from the first time where it is driven low during the duration of the transfer shows something is wrong.

Is there a known errata or problem in the SDK?

We have tried on the latest dev kit hardware and it exhibits this.

We are using SDK 11 from memory...