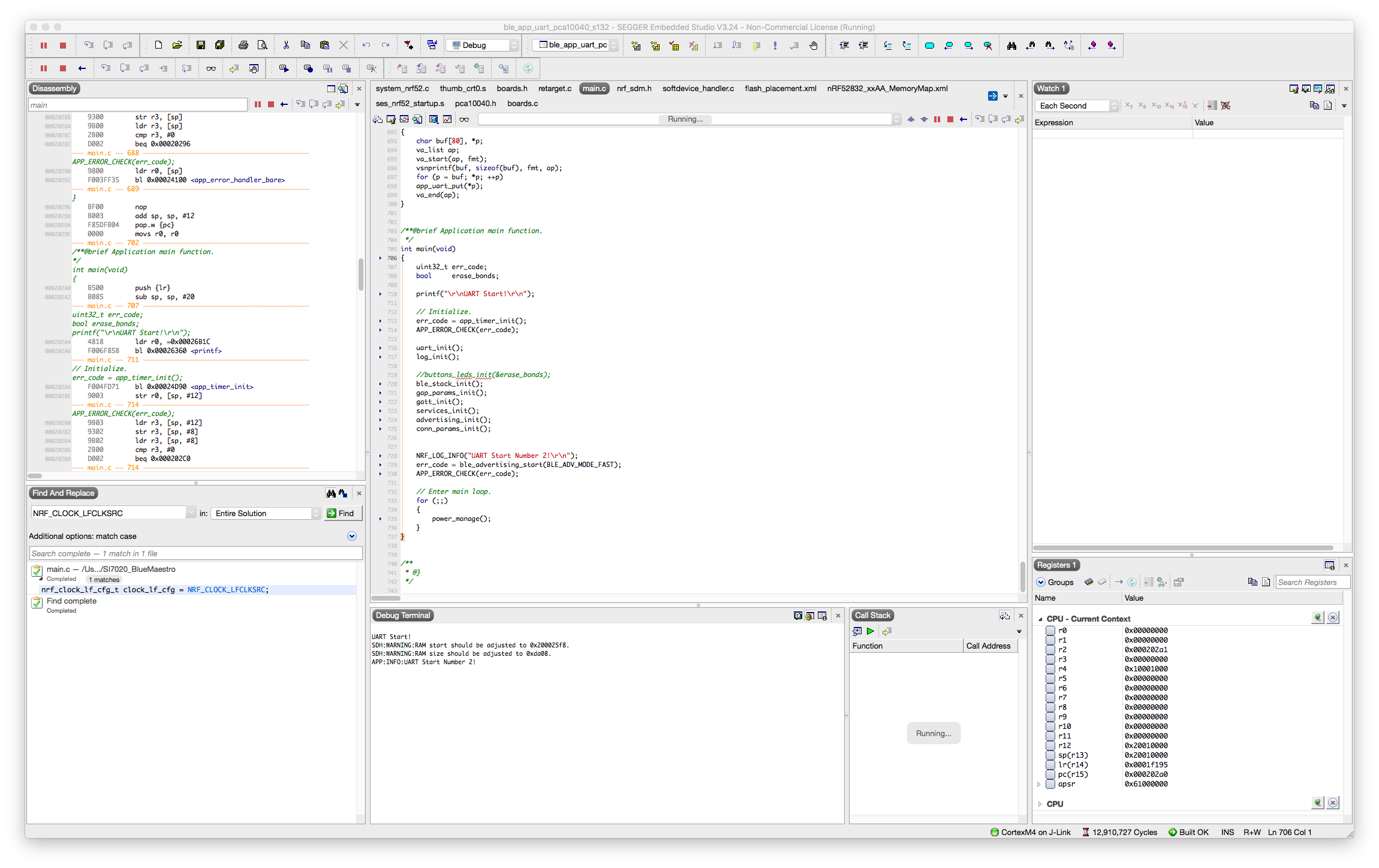

So I thought I would upgrade one of my projects to SDK13 and try out SES 3.24 at the same time. I thought I would start by getting the ble_app_uart_pca10040_s132 project to work first.

Alarmingly I am getting a strange warning on running the project as seen below. .

.

My MemoryMap.xml is

<!DOCTYPE Board_Memory_Definition_File> <root name="nRF52832_xxAA"> <MemorySegment name="FLASH" start="0x1f000" size="0x61000" access="ReadOnly" /> <MemorySegment name="SRAM" start="0x200025f8" size="0xda08" access="Read/Write" /> </root>

So SES is suggesting RAM needs to be adjusted to something it (or more specifically SRAM) already is.

Seeing this this makes me nervous that something isn't set up correctly that will come back to bite later.

This is nRF52832 QFAA s132 SD4.0.2.

Does anyone have any ideas here?