I am reading a large FIFO buffer from a sensor and there are at least two ways to do it - by simply reading the FIFO using the CPU and SPI in chunks of 255 byte blocks, or using EasyDma list (also chunked). Both using SPI @ 8mbps. This post outlines the EasyDma list setup for this scenario.

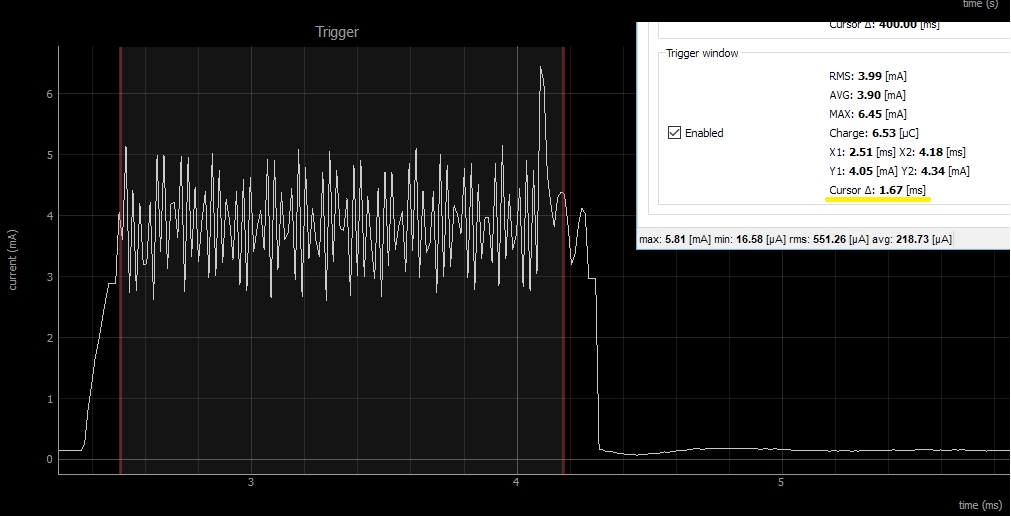

I've used the PPK to look at the differences in power usage. The EasyDma list approach does not seem to be any different in the power profile compared to just reading it using the CPU. I've included the PPK plot of one FIFO EasyDma list read. Using code to time the code path of one read, it takes about 1.6ms to read one FIFO buffer. This is correlated with the PPK plot. But there appears to be something keeping the consumption constantly around 3.9mA throughout that 1.6ms read. I expect the plot to drop significantly in the middle of a read and not remain constant throughout reading the FIFO.

I've verified that the main thread is blocked (for about 1.5ms) in one sd_app_evt_wait while waiting for the FIFO read to complete. Also, the read end event occurs once when its done. There is no BLE activity. When not in this read scenario, the power consumption remains low, around the sensors 160mA usage (very low line before and after the FIFO read in the plot). What else could be consuming this amount of power during the FIFO read ?