I have recently acquired a NAND chip from Micron and would like to use it for storage.

However, looking through the datasheet I found out that the addressing scheme require by the Micron chip is a bit different from the QSPI used in the SoC.

For READ, READ2O and READ4O, the pattern of the address bytes following the command byte are the same for the chip and the SoC, but for READ2IO and READ4IO, they are different.

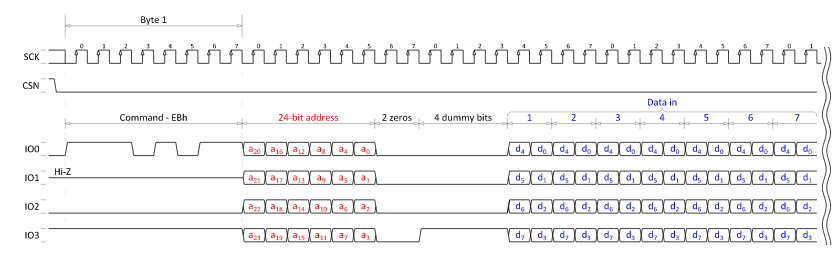

SoC QSPI:

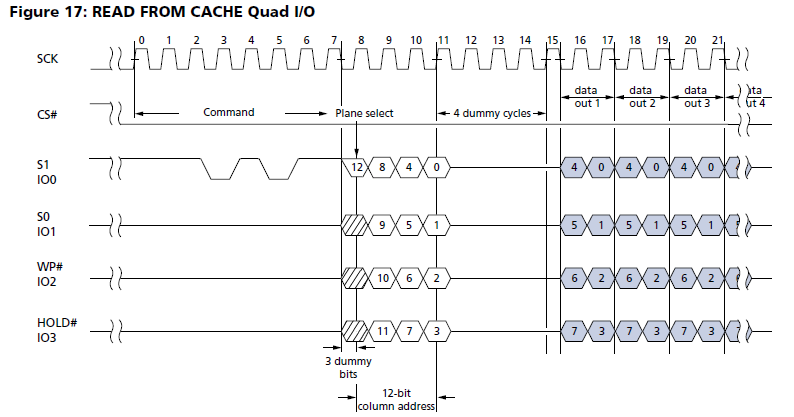

Micron chip:

Notice how the address required by the Micron chip is only 12 bits + 3 dummy bits. The same behavior goes for the write as well.

Is there a way to overcome this so that I can use IO operation instead of O on the chip?