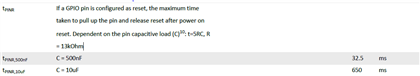

A time T_PINR is specified in the datasheet, as shown in the snippet below.

Does this give me an indication of the pulse width for a pin reset? If so, how do I interpret this value? If not, what does this specification refer to, and how long would I need to pull the reset pin low (from an external MCU) in order to accomplish a pin reset?