I'm getting errors on trying to program a custom board using the Laird BL654.

We are verifying manufacturing results with an x-ray of a populated board tomorrow checking for voids or shorts. While we're trying to rule out any manufacturing errors on our end, I wanted to get input on these programming errors.

We are verifying manufacturing results with an x-ray of a populated board tomorrow checking for voids or shorts. While we're trying to rule out any manufacturing errors on our end, I wanted to get input on these programming errors.

The two errors are visible in nRFgo Studio, nRF Connect's Programmer Tool, but also the nrfjprog command line.

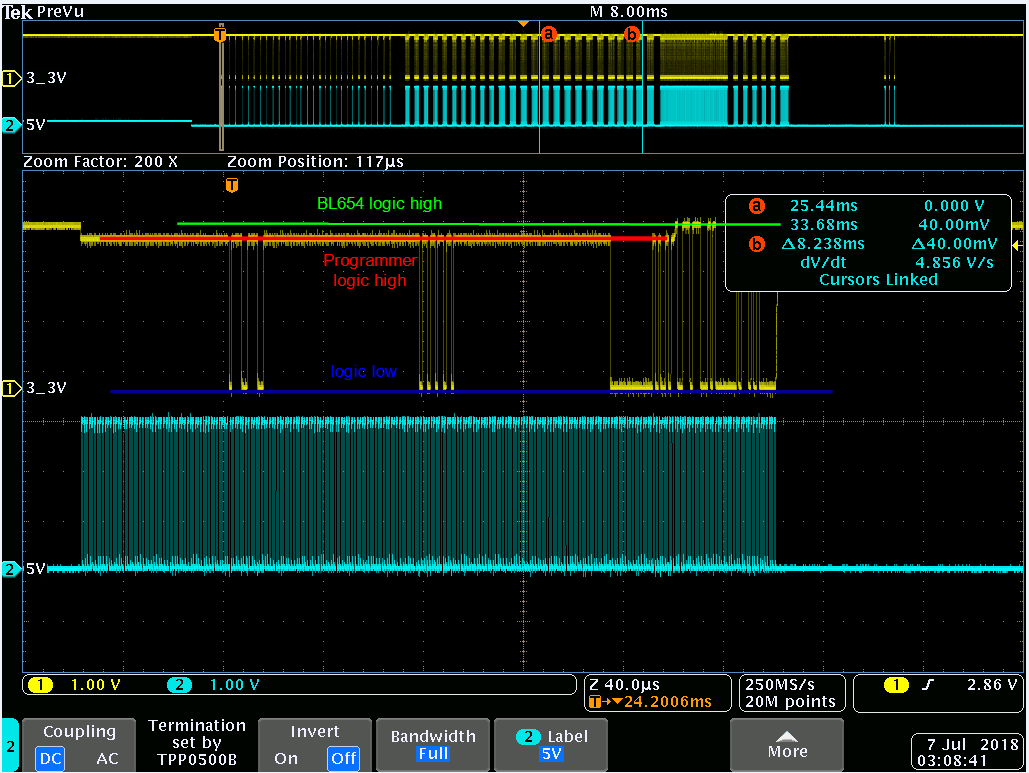

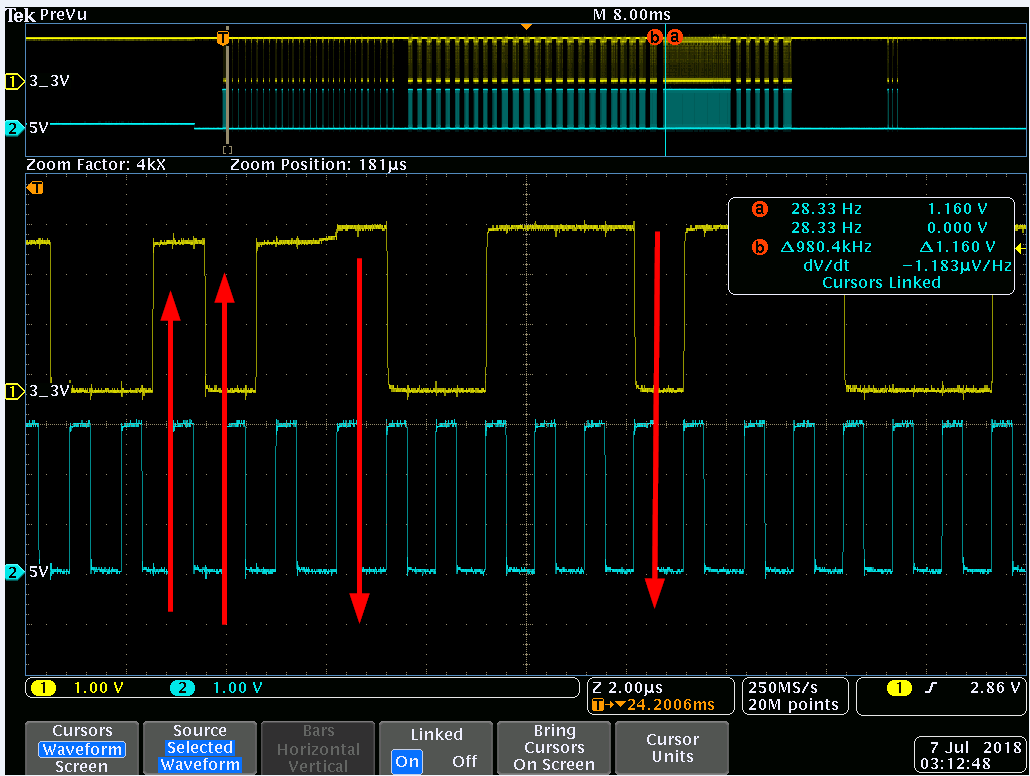

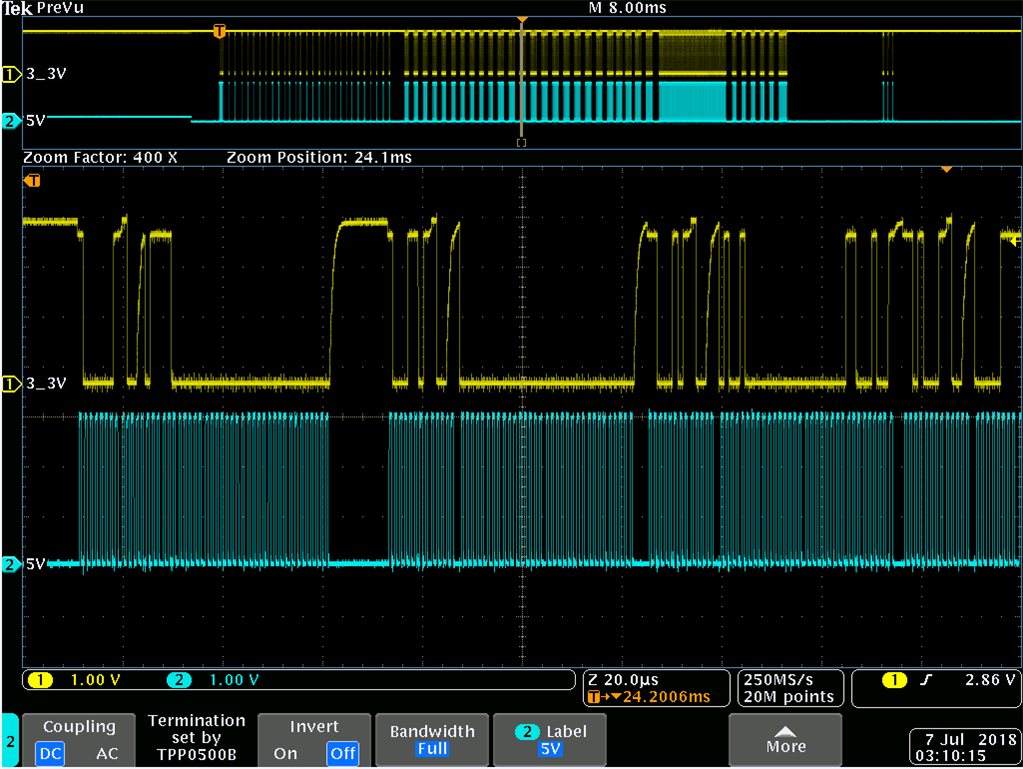

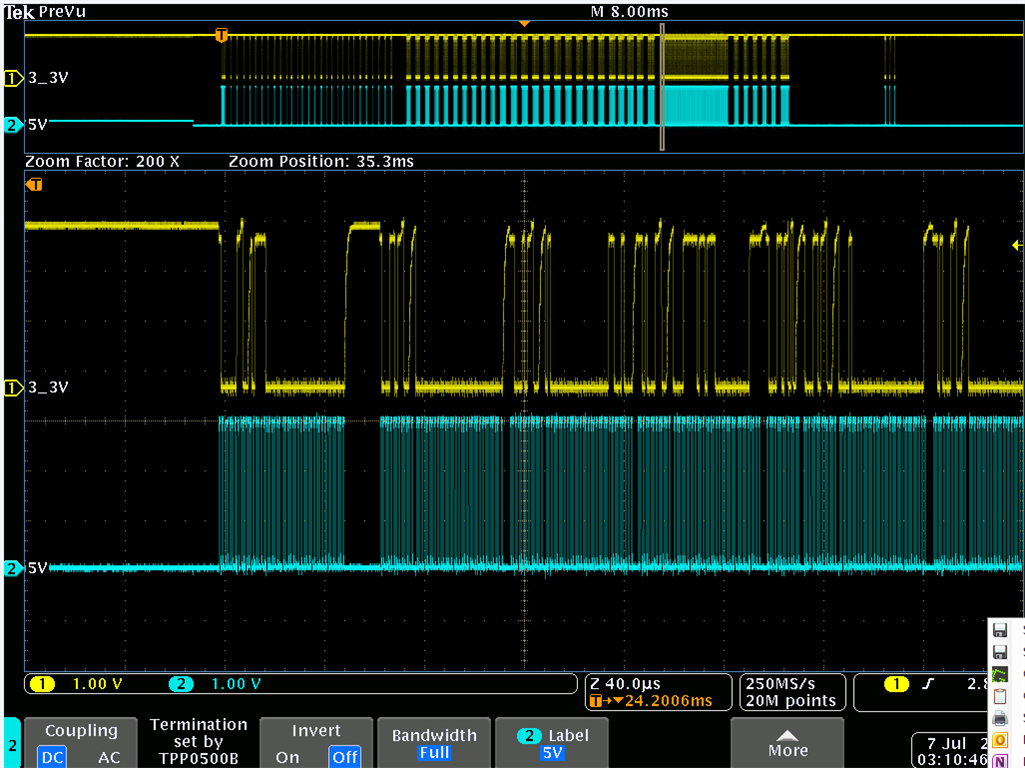

The SWDIO line has activity verified with scope.

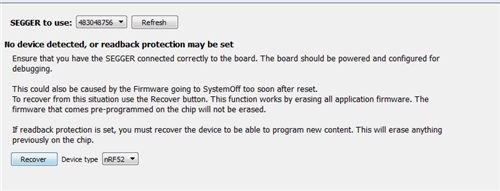

nRFgo Studio:

Clicking under "nRF52 development dongles -> Segger XXXXXX" Briefly Flashes:

And then the segger tool ejects from Windows and tries to re-mount as a drive. Recovery fails.

nRF Connect Programmer App:

Error when getting device info: Error: Error occured when open device long term. Errorcode: CouldNotOpenDevice (0x4) Lowlevel error: JLINKARM_DLL_ERROR (ffffff9a)

Error when closing nrfjprog: Error: Error occured when close opened device. Errorcode: CouldNotOpenDevice (0x4) Lowlevel error: JLINKARM_DLL_ERROR (ffffff9a)

I've also seen 'NOT_AVAILABLE_BECAUSE_PROTECTION' which in the documentation states that readback protection is enabled. Recovery attempts again do not work.

CMD.exe (nrfjprog 9.7.3 / JLinkARM.dll 6.22g):

Trying to run recover, eraseall or trying to connect throws this error:

ERROR: JLinkARM DLL reported an error. Try again. If error condition

ERROR: persists, run the same command again with argument --log, con

ERROR: Semiconductor and provide the generated log.log file to them.

Any help would be greatly appreciated,

Any help would be greatly appreciated,

Jeff