Hello,

I am using nRF52840 with nRF5_SDK_15.0.0_a53641a.

I am looking at the QSPI example which I have slightly modified so that after the write of 256 bytes, it enters into a loop reading continiously 64 bytes from the external Flash.

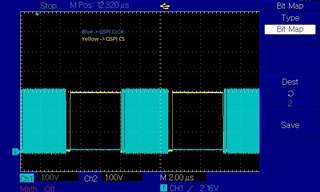

To read 64 bytes with 32MHz clock requires about 4.4usec with the QSPI.

My code looks like this:

while(1)

{nrfx_err=nrfx_qspi_read(m_buffer16_rx, 64, 0);

WAIT_FOR_PERIPH();

}

I am noticing an 4.5 to 6usec latency between the end of read (i.e CS goes high) till the next read cycle begins.

Any explanation about this latency? Is due to the Flash or is the MCU peripheral actually doing something in that time?

Thank you for your answers.