Hi

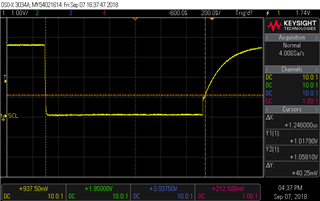

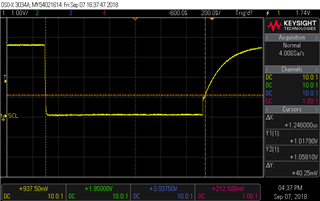

We met the problem is that clock low time period is out of spec, we got the value from oscilloscope is 1.24us@pull up resistor 10K/7.15k when clock speed=400kHz. The spec is >1.3us.

can we modify the timing in SW? How to modify it?

thanks,

Hi

We met the problem is that clock low time period is out of spec, we got the value from oscilloscope is 1.24us@pull up resistor 10K/7.15k when clock speed=400kHz. The spec is >1.3us.

can we modify the timing in SW? How to modify it?

thanks,

Hi,

There is no way to adjust this in software. I see that the minimum tLOW is 1.3 μs for Fast-mode I2C devices in the I2C spec, so I would have expected the nRF to stay within that. Which high frequency clock source do you use when you see this (RC or xtal)?

We using external 32 MHz crystal, HFCLK. The Open-drain pulling low or "release can be controlled by master, not sure why we can't adjust the timing on this?

There is no way to adjust the timing on the clock signal. If you only see this on the first pulse after clock stretching, it may be due to erratum 149. I have not been able to find any reports of this causing problems with any I2C slaves in practice, though.

It depends on the micro. The nRF52840 does have a frequency setting. See their errata.

It does cause a problem with some slave devices, especially some accelerometers. It causes the SDA line to be stuck low.