Hi Guys,

I'm interested to get guideline on how could I customized the qspi example from nordic in terms of pins and command. I don't see any different between MX25R6435F vs S25FL064L chipset

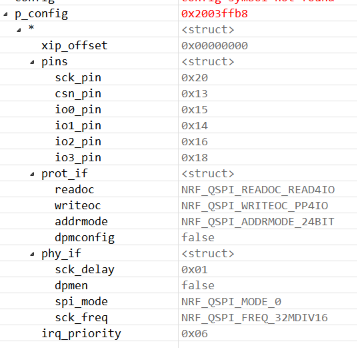

I was trying to change the qspi example code and unsuccessful control the qspi using the following setting.

#define QSPI_CSN NRF_GPIO_PIN_MAP(0,19) #define QSPI_IO0 NRF_GPIO_PIN_MAP(0,21) #define QSPI_IO1 NRF_GPIO_PIN_MAP(0,20) #define QSPI_IO2 NRF_GPIO_PIN_MAP(0,22) #define QSPI_IO3 NRF_GPIO_PIN_MAP(0,24) #define QSPI_SCK NRF_GPIO_PIN_MAP(1,0)

And the I did some change to some of the header as below

nrfx_qspi.h

#define NRFX_QSPI_DEFAULT_CONFIG \

{ \

.xip_offset = NRFX_QSPI_CONFIG_XIP_OFFSET, \

.pins = { \

.sck_pin = QSPI_PIN_SCK, \

.csn_pin = QSPI_PIN_CSN, \

.io0_pin = QSPI_PIN_IO0, \

.io1_pin = QSPI_PIN_IO1, \

.io2_pin = QSPI_PIN_IO2, \

.io3_pin = QSPI_PIN_IO3, \

}, \

.irq_priority = (uint8_t)NRFX_QSPI_CONFIG_IRQ_PRIORITY, \

.prot_if = { \

.readoc = (nrf_qspi_readoc_t)NRFX_QSPI_CONFIG_READOC, \

.writeoc = (nrf_qspi_writeoc_t)NRFX_QSPI_CONFIG_WRITEOC, \

.addrmode = (nrf_qspi_addrmode_t)NRFX_QSPI_CONFIG_ADDRMODE, \

.dpmconfig = false, \

}, \

.phy_if = { \

.sck_freq = (nrf_qspi_frequency_t)NRFX_QSPI_CONFIG_FREQUENCY, \

.sck_delay = (uint8_t)NRFX_QSPI_CONFIG_SCK_DELAY, \

.spi_mode = (nrf_qspi_spi_mode_t)NRFX_QSPI_CONFIG_MODE, \

.dpmen = false \

}, \

}

nrf_drv_qspi.h

#if QSPI_PIN_SCK == NRF_QSPI_PIN_NOT_CONNECTED

#undef QSPI_PIN_SCK

#define QSPI_PIN_SCK QSPI_PIN_SCK

#endif

#if QSPI_PIN_CSN == NRF_QSPI_PIN_NOT_CONNECTED

#undef QSPI_PIN_CSN

#define QSPI_PIN_CSN QSPI_PIN_CSN

#endif

#if QSPI_PIN_IO0 == NRF_QSPI_PIN_NOT_CONNECTED

#undef QSPI_PIN_IO0

#define QSPI_PIN_IO0 QSPI_PIN_IO0

#endif

#if QSPI_PIN_IO1 == NRF_QSPI_PIN_NOT_CONNECTED

#undef QSPI_PIN_IO1

#define QSPI_PIN_IO1 QSPI_PIN_IO1

#endif

#if QSPI_PIN_IO2 == NRF_QSPI_PIN_NOT_CONNECTED

#undef QSPI_PIN_IO2

#define QSPI_PIN_IO2 QSPI_PIN_IO2

#endif

#if QSPI_PIN_IO3 == NRF_QSPI_PIN_NOT_CONNECTED

#undef QSPI_PIN_IO3

#define QSPI_PIN_IO3 QSPI_PIN_IO3

#endif

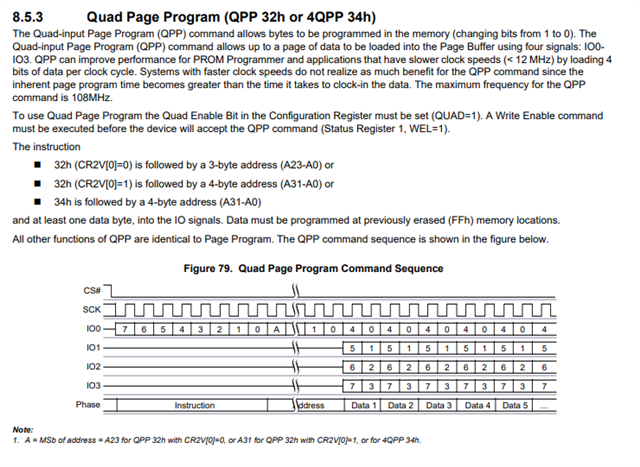

Target memory chip to use.