Hi,

I was trying to communicate with an I2C device, which's address is 0x7C

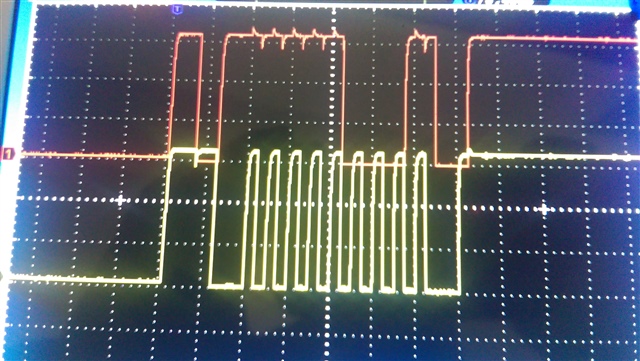

But I always got NRF_DRV_TWI_EVT_ADDRESS_NACK event, so I took a check on the TWI wave:

Looks like the signal on SDA is correct but the SCK signal is 1 cycle later than normal, that make 0x7C as 0x80.

Why this could happen? is it an issue missed in errata?

Note: I noticed there's DMA issue in errata so I choosed TWI instead of TWIM