Hello,

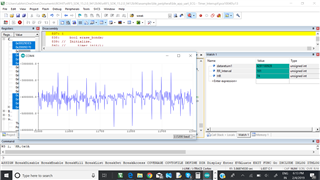

As I am using max30003 ECG with nrf52840 Using NRFX_SPIM example code( SDK15.2-PCA100056 ), I have developed drivers and I am able to read device id through my driver successfully. I have also done reading and writing on all registers except ECG_FIFO.

I have referred MAX 30003 ECG driver which is given by MAXIM.

in Nrfx_spim coding, I have changed spi_config.orc from 0xFF to 0x00 to avoid overrun error.

but I unable to get data in my Receiver buffer.

kindly compare the MAXIM Drivers and NRF_SPIM codes below and help me find the error I am trying my best since past 2 months but unable to find the error it will be great if we are able to do this together and the project will be successfully finished since this is the only part of code remaining.

NRF CODE:

In Reg_READ Function:

if I Change from xfer_desc.rx_length = 3; to xfer_desc.rx_length = 4;

Then i got some data in Receiver Buffer.

Let Me know This changes is correct or not?

NOTE: PLEASE MAKE IT PRIVATE THREAD

Thanks and Regards,

Rohit

#include "nrfx_spim.h"

#include "app_util_platform.h"

#include "nrf_gpio.h"

#include "nrf_delay.h"

#include "boards.h"

#include "app_error.h"

#include <string.h>

#include "nrf_log.h"

#include "nrf_log_ctrl.h"

#include "nrf_log_default_backends.h"

#include "MAX30003.h"

#define NRFX_SPIM_SCK_PIN 3

#define NRFX_SPIM_MOSI_PIN 4

#define NRFX_SPIM_MISO_PIN 28

#define NRFX_SPIM_SS_PIN 29

#define NRFX_SPIM_DCX_PIN 30

#define SPI_INSTANCE 3 /**< SPI instance index. */

const nrfx_spim_t spi = NRFX_SPIM_INSTANCE(SPI_INSTANCE); /**< SPI instance. */

volatile bool spi_xfer_done; /**< Flag used to indicate that SPI instance completed the transfer. */

uint8_t m_tx_buf[4]; //= {0xff,0x01,0x02}; // ={0x0F}; // 32 bit transfers

uint8_t m_rx_buf[sizeof(m_tx_buf)]; /**< RX buffer. */

const uint8_t m_length = sizeof(m_tx_buf); /**< Transfer length. */

nrfx_spim_xfer_desc_t xfer_desc; //=NRFX_SPIM_XFER_TRX(m_tx_buf, 1, m_rx_buf, 3);

nrfx_spim_config_t spi_config = NRFX_SPIM_DEFAULT_CONFIG;

uint32_t stored[200];

uint16_t i;

uint32_t valid_data[200];

void spim_event_handler(nrfx_spim_evt_t const * p_event,

void * p_context)

{

spi_xfer_done = true;

NRF_LOG_INFO("Transfer completed.");

if (m_rx_buf[0] != 0)

{

NRF_LOG_INFO(" Received:");

NRF_LOG_HEXDUMP_INFO(m_rx_buf, strlen((const char *)m_rx_buf));

}

}

uint32_t MAX30003_Reg_Write(uint8_t Reg_address, uint32_t data)

{

nrfx_err_t err_code = 0;

//Prepare the tx buffer

memset(m_rx_buf, 0x00, sizeof(m_rx_buf)); // Erases the buffer

m_tx_buf[0] = ((Reg_address << 1) | 0x00);

//Create the transfer descriptor

xfer_desc.p_tx_buffer=m_tx_buf;

xfer_desc.tx_length = 4;

xfer_desc.p_rx_buffer=NULL;

xfer_desc.rx_length = NULL;

spi_xfer_done = false;

spi_config.orc=0x00;

m_tx_buf[1] = (data >> 16);

m_tx_buf[2] = (data >> 8);

m_tx_buf[3] = (data);

err_code = nrfx_spim_xfer(&spi, &xfer_desc, 0);

APP_ERROR_CHECK(err_code);

while (spi_xfer_done == false);

// return data;

}

void max30003_sw_reset(void)

{

MAX30003_Reg_Write(SW_RST,0x000000);

nrf_delay_ms(100);

}

void max30003_synch(void)

{

MAX30003_Reg_Write(SYNCH,0x000000);

}

void MAX30003_begin()

{

max30003_sw_reset();

MAX30003_Reg_Write(CNFG_GEN,0x080000);

nrf_delay_ms(100);

MAX30003_Reg_Write(CNFG_CAL, 0x000000 ); // 0x700000

nrf_delay_ms(100);

MAX30003_Reg_Write(CNFG_EMUX,0x000000 );

nrf_delay_ms(100);

MAX30003_Reg_Write(CNFG_ECG, 0x805000 ); //

nrf_delay_ms(100);

MAX30003_Reg_Write(CNFG_RTOR1,0x3fc600);

max30003_synch();

nrf_delay_ms(100);

}

uint32_t MAX30003_Reg_Read(uint8_t Reg_address)

{

nrfx_err_t err_code = 0;

uint32_t data=0;

//Prepare the tx buffer

memset(m_rx_buf, 0x00, sizeof(m_rx_buf)); // Erases the buffer

m_tx_buf[0] = ((Reg_address << 1) | 0x01);

//Initiate the transfer

xfer_desc.p_tx_buffer=m_tx_buf;

xfer_desc.tx_length = 1;

nrf_delay_ms(5);

xfer_desc.p_rx_buffer=m_rx_buf;

xfer_desc.rx_length = 3;

spi_config.orc=0x00;

spi_xfer_done = false;

err_code = nrfx_spim_xfer(&spi, &xfer_desc, 0);

APP_ERROR_CHECK(err_code);

while (spi_xfer_done == false);

data |= (m_rx_buf[0] << 16);

data |= (m_rx_buf[1] << 8);

data |= m_rx_buf[2];

return data;

}

int main(void)

{

bsp_board_init(BSP_INIT_LEDS);

APP_ERROR_CHECK(NRF_LOG_INIT(NULL));

NRF_LOG_DEFAULT_BACKENDS_INIT();

//nrfx_spim_config_t spi_config = NRFX_SPIM_DEFAULT_CONFIG;

spi_config.frequency = NRF_SPIM_FREQ_4M;

spi_config.ss_pin = NRFX_SPIM_SS_PIN;

spi_config.miso_pin = NRFX_SPIM_MISO_PIN;

spi_config.mosi_pin = NRFX_SPIM_MOSI_PIN;

spi_config.sck_pin = NRFX_SPIM_SCK_PIN;

//spi_config.dcx_pin = NRFX_SPIM_DCX_PIN;

spi_config.use_hw_ss = true;

spi_config.ss_active_high = false;

spi_config.mode = NRF_SPIM_MODE_0; // SCK active high, sample on leading edge of clock, CPOL=0/CPHA=0

spi_config.bit_order=NRF_SPIM_BIT_ORDER_MSB_FIRST;

spi_config.orc=0x00;

APP_ERROR_CHECK(nrfx_spim_init(&spi, &spi_config, spim_event_handler, NULL));

NRF_LOG_INFO("NRFX SPIM example started.");

MAX30003_begin();

while (1)

{

// Reset rx buffer and transfer done flag

memset(m_rx_buf, 0, m_length);

spi_xfer_done = false;

for(i=0;i<=200;i++)

{

nrf_delay_ms(10);

stored[i]=MAX30003_Reg_Read(ECG_FIFO); //0x0F

stored[i]=stored[i] <<8;

valid_data[i] = (((uint8_t)stored[i])>>3)&0x07;

}

while (!spi_xfer_done)

{

__WFE();

}

NRF_LOG_FLUSH();

bsp_board_led_invert(BSP_BOARD_LED_0);

//nrf_delay_ms(200);

}

}

MAXIM Drivers

#include "MAX30003.h"

MAX30003::MAX30003(SPI &spiBus, PinName cs):

m_spiBus(spiBus), m_cs(cs, 1)

{

}

MAX30003::~MAX30003()

{

//empty block

}

uint32_t MAX30003::readRegister(const Registers_e reg)

{

uint32_t data = 0;

m_cs = 0;

m_spiBus.write((reg << 1) | 1);

data |= (m_spiBus.write(0xFF) << 16);

data |= (m_spiBus.write(0xFF) << 8);

data |= m_spiBus.write(0xFF);

m_cs = 1;

return data;

}

void MAX30003::writeRegister(const Registers_e reg, const uint32_t data)

{

m_cs = 0;

m_spiBus.write(reg << 1);

m_spiBus.write((0x00FF0000 & data) >> 16);

m_spiBus.write((0x0000FF00 & data) >> 8);

m_spiBus.write( 0x000000FF & data);

m_cs = 1;

}