I am trying to run the SPI code on an NRF52382 based custom board. I am using the NRF 52 DK, Keil uVision 5.0 , SDK 15.2.

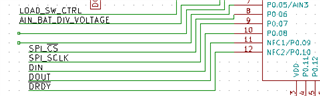

I cannot set and clear the SPI relevant pins on my custom board as gpios. The pins I am using are:

SPI_SS_PIN = P0.6

SPI_MISO_PIN = P0.8

SPI_MOSI_PIN = P0.9

SPI_SCK_PIN = P0.7

and the schematic showing these pins is:

I was successfully able to toggle all four pins above, (as well as the RESET P0.21) as GPIOs after I did following:

1. went to sdk_config.h and changed NRF_LOG_BACKEND_UART_TX_PIN to pin 5 instead of 6

2. went to OPTIONS FOR TARGET -> C/C++ -> Preprocessor Symbols -> Define and added " CONFIG_NFCT_PINS_AS_GPIOS" after nrf52382.... and removed the line " CONFIG_GPIO_AS_PINRESET"

But as soon as I run the SPI example code in SDK15 I am unable to toggle these pins and use them as gpios. Especially the SPI_SS_PIN which is pin 6, as soon as I run the SPI code this pin fixes to high value and will not clear/go low.

My thinking is there something wrong with the way the SPI example configures the spi relevant pins?

https://devzone.nordicsemi.com/f/nordic-q-a/18546/gpio-not-set-or-clear-with-spi-code this guy seemed to have had the same problem running SPI and with the CS pin...

Thank you!