Does the nrf52832 has some delay when the shortcut of END_START is enabeled in continuous receiving?What is the meaning of rx chain delay?Does RX chain delay in 2Msps mode is 5us or 9.4us?

Does the nrf52832 has some delay when the shortcut of END_START is enabeled in continuous receiving?What is the meaning of rx chain delay?Does RX chain delay in 2Msps mode is 5us or 9.4us?

Hi,

Unfortunately we do not have any numbers for this, I would expect it to be <1 µs. t_RXCHAIN is the time from a bit appears as energy on the ANT pin to the radio peripheral is aware of it, so that is not relevant.

Best regards,

Andreas

Hi,

Thanks!Before I post the questions,I also browse some related Q&A.Some descriptions about rx chain delay seem differen as yours.Here are some links:

devzone.nordicsemi.com/.../what-is-rx-tx-chain-delay

devzone.nordicsemi.com/.../113978

Someone said: In other words you should be fine as long as there is a 10us delay between the end of the CRC of the first packet, and the start of the address of the second packet.

I'm so confused about the exact that.

Hi,

Thanks a lot!

I use one nrf52 chip to transmit consecutive packets with 1us interframe spacing in 2Mbps mode and use a timer to collect all end times for compare.The RX chip can receive the packets with the whole rx chain delay 5us and packets with 1us spacing.

Now I have another question:when several chips transmit packets one by one,should they have a inter spacing?Or just as the one chip transmitting consecutive packets ?

I'm looking forward your reply.Because it is important for my future developement.If there must be some inter spacing time among serveral chips,I must add the spacing time between consecutive packets from different chips.

Hi,

If I understand correctly you should probably add the 5µs delay between the transmitted packets just so that you are certain the receiver is ready for the next one. (I am not 100% sure how it likes to receive two packets within the same receive event) Feel free to try sending without any interspacing though, it might work and you will not break anything.

Best regards,

Andreas

Hi,

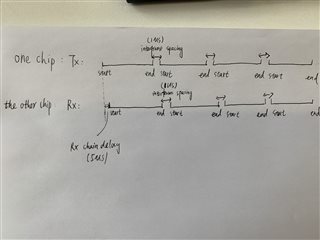

Thanks a lot!Maybe my description is not clear to understand.I already use one nrf52 chip to transmit consecutive packets with 1us interframe spacing in 2Mbps mode,and the receiver can receive the the first packet is delayed to 5us and the following packets with 1us interframe spacing.The diagram is as below:

However,when I use four different tx chips with the interframe spacing (1us ~ 10us),the receiver can not succeed in receiving all the packets.So my main trouble is the difference between one chip and several chips when sending consecutive packets.Is the tx end the same tine with the receive end besides rx whole rx chain delay?

Hi,

jane_song said:So my main trouble is the difference between one chip and several chips when sending consecutive packets.Is the tx end the same tine with the receive end besides rx whole rx chain delay?

If I understand you correctly, TX end will happen t_TOF + t_RXchain before RX end, where t_TOF is the time of flight, and t_RXchain is the RX chain delay. t_TOF should be neglible unless there is a significant distance between the devices.

Best regards,

Andreas

Hi,

Thanks a lot!The t_TOFis a neccassry time between tx side and rx side and I take into consideration of that.I‘m still confused about that one chip and several chips when sending consecutive packets.

Hi,

Thanks a lot!The t_TOFis a neccassry time between tx side and rx side and I take into consideration of that.I‘m still confused about that one chip and several chips when sending consecutive packets.