I'm developing IO-Link driver using UARTE peripherial.

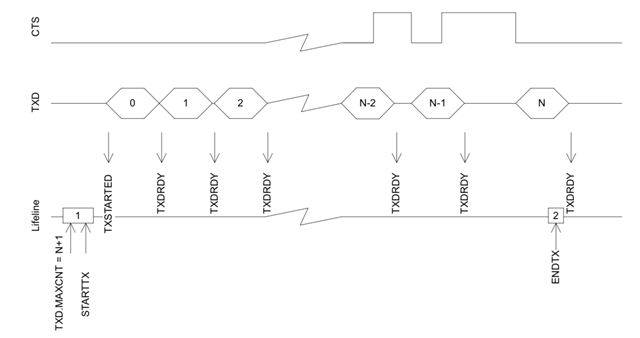

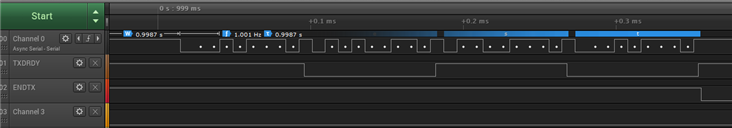

Is it possible to get event on end of transmition with EasyDMA Tx. Event ENDTX is fired before all transmited bytes are send.

Second question: Is it possible to disable Rx line while transmiting on Tx? IO-link phy layer is single line and every Tx char is reflected on Rx line.

Why I get characters received in rx buffer even when TASK_STARTRX is not fired?