I am using the SPIM example in the nRF52840 SDK. It uses SPI_INSTANCE 3. I am doing a simple SPI Write of 2 bytes.

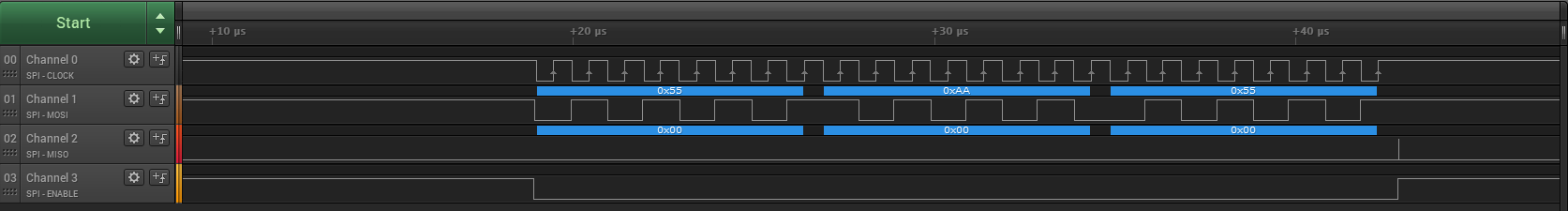

I get SS, SCK, working properly. MOSI is transitioning but it is not related to anything in the Tx buffer. I have tried both NRFX_SPIM_XFER_TRX and NRFX_SPIM_XFER_TX function calls.

Any help would be appreciated.

Below is an excerpt of some of the relevant code:

m_tx_buf[0] = 0x55; /**< TX buffer. */

m_tx_buf[1] = 0xAA; /**< TX buffer. */

m_tx_buf[2] = 0x55; /**< TX buffer. */

m_rx_buf[0] = 0x11; /**< TX buffer. */

m_rx_buf[1] = 0x66; /**< TX buffer. */

m_rx_buf[2] = 0x11; /**< TX buffer. */

tx_length = 2; /**< Transfer length. */

rx_length = 0; /**< Transfer length. */

// nrfx_spim_xfer_desc_t xfer_desc_WREN = NRFX_SPIM_XFER_TX(m_tx_buf, tx_length);

nrfx_spim_xfer_desc_t xfer_desc_WREN = NRFX_SPIM_XFER_TRX(m_tx_buf, tx_length, m_rx_buf, rx_length);

----------------------------

nrfx_spim_config_t spi_config = NRFX_SPIM_DEFAULT_CONFIG;

spi_config.frequency = NRF_SPIM_FREQ_1M;

spi_config.ss_pin = NRFX_SPIM_SS_PIN;

spi_config.miso_pin = NRFX_SPIM_MISO_PIN;

spi_config.mosi_pin = NRFX_SPIM_MOSI_PIN;

spi_config.sck_pin = NRFX_SPIM_SCK_PIN;

spi_config.mode = NRF_SPIM_MODE_3; // clk normally high, rising edge

spi_config.bit_order = NRF_SPIM_BIT_ORDER_MSB_FIRST;

// spi_config.dcx_pin = NRFX_SPIM_DCX_PIN;

spi_config.use_hw_ss = true;

spi_config.ss_active_high = false;

APP_ERROR_CHECK(nrfx_spim_init(&spi, &spi_config, spim_event_handler, NULL));

----------------------------------

while (1)

{

// Reset rx buffer and transfer done flag

// memset(m_rx_buf, 0, rx_length);

spi_xfer_done = false;

APP_ERROR_CHECK(nrfx_spim_xfer(&spi, &xfer_desc_WREN, 0));

while (!spi_xfer_done)

{

_ _WFE();

}

}