Misc info:

1. SDK Version: v15.3

2. SD: 6.1.1

3. Toolchain: IAR v7

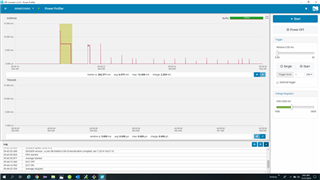

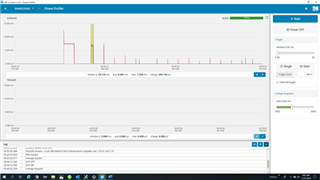

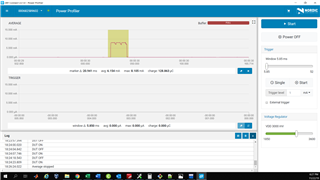

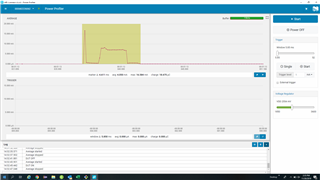

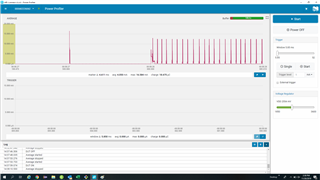

I'm trying to use secure_bootloader from the examples but it's taking higher current upon power on.

Our intention is to integrate the bootloader with the soft device+application but higher current consumption is an issue.

Please check the attached images which we got from PPK.

Can you please help me out on this?