用nRF5SDK160098a08e2里面的spis工程在52832开发板上跑,但数据发送不正常

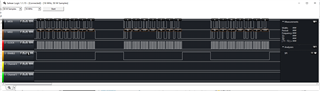

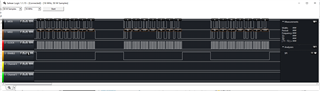

1,从逻辑分析仪图上看,spi主的时序没问题,发送的数据内容也没问题,但MISO这跟线的数据经常发不完整

用nRF5SDK160098a08e2里面的spis工程在52832开发板上跑,但数据发送不正常

1,从逻辑分析仪图上看,spi主的时序没问题,发送的数据内容也没问题,但MISO这跟线的数据经常发不完整

Hi,

Do you mean nRF52832DK MISO sent incomplete data while executing the SDK 16/spis example? If so, which pin are you using for MISO on Slave and Master boards?

-Amanda H.

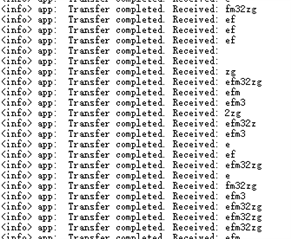

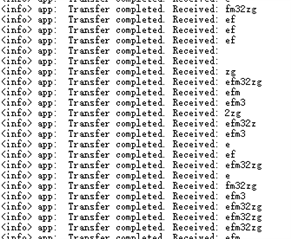

Yes, in the example, the MISO pin is p0.30, but i use the silicon's efm32zgf32 to work as the Master spi。

Hi,

Did you modify the spis example code? If so, what is that? Could you share with us?

I tested two nRF52832DKs with SPI Master Example and SPI Slave Example, and I could not reproduce the problem.

-Amanda H.

I also test other three situations(nRF52832DK as SPIM with nRF52832DK as SPIS,nRF52832DK as SPIM with efm32 as SPIS, efm32 as SPIM with efm32 as SPIS), they all work well, only use efm32 as SPIM with nRF52832DK as SPIS, it make mistake。

efm32 means efm32zg210f32

my nRF52832DK code file and efm32zg210f32 code file。

#include "em_device.h"

#include "em_chip.h"

//#include "hal-config.h"

#include <stdint.h>

#include <stdbool.h>

//#include "efm32.h"

//#include "efm32_chip.h"

#include "em_cmu.h"

#include "em_gpio.h"

#include "em_usart.h"

#define autoCS 0

#define PIN_CS 14

#define PORT_CS gpioPortC

static uint8_t spis_idx = 0;

void SPI_Initial(bool master)

{

CMU_ClockEnable(cmuClock_HFPER, true);

CMU_ClockEnable(cmuClock_GPIO, true);

CMU_ClockEnable(cmuClock_USART1, true);

USART_InitSync_TypeDef SPI_init = USART_INITSYNC_DEFAULT;

// SPI_init.baudrate = 1000000;

SPI_init.autoCsEnable = autoCS;

SPI_init.msbf = true;

SPI_init.master = master;

USART_InitSync(USART1, &SPI_init);

if (master)

{

GPIO_PinModeSet(gpioPortD, 7, gpioModePushPull, 0); //MO

GPIO_PinModeSet(gpioPortD, 6, gpioModeInput, 0); //MI

GPIO_PinModeSet(gpioPortC, 15, gpioModePushPull, 0); //clk

GPIO_PinModeSet(PORT_CS, PIN_CS, gpioModePushPull, 1); //cs

GPIO_DriveModeSet(PORT_CS,gpioDriveModeHigh);

}

else

{

GPIO_PinModeSet(gpioPortD, 7, gpioModeInput, 0); //MO

GPIO_PinModeSet(gpioPortD, 6, gpioModePushPull, 1); //MI

GPIO_PinModeSet(gpioPortC, 15, gpioModeInput, 0); //clk

GPIO_PinModeSet(PORT_CS, PIN_CS, gpioModeInput, 1); //cs

}

#if autoCS

USART1->ROUTE |= USART_ROUTE_CSPEN;

#endif

if(!master)

USART1->ROUTE |= USART_ROUTE_CSPEN;

USART1->ROUTE |= USART_ROUTE_CLKPEN | USART_ROUTE_TXPEN

| USART_ROUTE_RXPEN | USART_ROUTE_LOCATION_LOC3;

}

void delay(uint32_t count)

{

while (count--)

;

}

void CSBegin(void)

{

#if !autoCS

GPIO_PinOutClear(PORT_CS, PIN_CS);

delay(40);

#endif

}

void CSEnd(void)

{

#if !autoCS

delay(40);

GPIO_PinOutSet(PORT_CS, PIN_CS);

#endif

}

void test1by1(void)

{

for (int i = 0; i < 256; i++)

{

CSBegin();

USART_SpiTransfer(USART1, i & 0xff);

CSEnd();

}

}

void test256(void)

{

CSBegin();

for (int i = 0; i < 256; i++)

{

USART_SpiTransfer(USART1, i & 0xff);

}

CSEnd();

}

void teststr(void)

{

char *pStr = "efm32zgM";

CSBegin();

for (int i = 0; i < strlen(pStr); i++)

{

// USART_SpiTransfer(USART1, *(pStr + i));

USART_Tx(USART1, *(pStr + i));

}

CSEnd();

}

void spiM(void)

{

SPI_Initial(true);

/* Infinite loop */

while (1)

{

// test1by1();

teststr();

delay(10000);

}

}

void spiS(void)

{

char *pStr = "efm32zgS901234";

uint8_t len = strlen(pStr);

SPI_Initial(false);

while(1)

{

uint8_t tx = 0xAA;

if(spis_idx < len)

tx = *(pStr + spis_idx++);

else

spis_idx = 0;

USART_Tx(USART1, tx);

// if(USART1->IF & USART_IF_TXUF)

// {

// spis_idx = 0;

// }

}

}

int main(void)

{

/* Chip errata */

CHIP_Init();

SystemCoreClockUpdate();

// spiS();

spiM();

}

/**

* Copyright (c) 2015 - 2019, Nordic Semiconductor ASA

*

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without modification,

* are permitted provided that the following conditions are met:

*

* 1. Redistributions of source code must retain the above copyright notice, this

* list of conditions and the following disclaimer.

*

* 2. Redistributions in binary form, except as embedded into a Nordic

* Semiconductor ASA integrated circuit in a product or a software update for

* such product, must reproduce the above copyright notice, this list of

* conditions and the following disclaimer in the documentation and/or other

* materials provided with the distribution.

*

* 3. Neither the name of Nordic Semiconductor ASA nor the names of its

* contributors may be used to endorse or promote products derived from this

* software without specific prior written permission.

*

* 4. This software, with or without modification, must only be used with a

* Nordic Semiconductor ASA integrated circuit.

*

* 5. Any software provided in binary form under this license must not be reverse

* engineered, decompiled, modified and/or disassembled.

*

* THIS SOFTWARE IS PROVIDED BY NORDIC SEMICONDUCTOR ASA "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY, NONINFRINGEMENT, AND FITNESS FOR A PARTICULAR PURPOSE ARE

* DISCLAIMED. IN NO EVENT SHALL NORDIC SEMICONDUCTOR ASA OR CONTRIBUTORS BE

* LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

* CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE

* GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION)

* HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

* LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT

* OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include "sdk_config.h"

#include "nrf_drv_spis.h"

#include "nrf_gpio.h"

#include "boards.h"

#include "app_error.h"

#include <string.h>

#include "nrf_log.h"

#include "nrf_log_ctrl.h"

#include "nrf_log_default_backends.h"

#define SPIS_INSTANCE 1 /**< SPIS instance index. */

static const nrf_drv_spis_t spis = NRF_DRV_SPIS_INSTANCE(SPIS_INSTANCE);/**< SPIS instance. */

#define TEST_STRING "Nordic"

static uint8_t m_tx_buf[] = TEST_STRING; /**< TX buffer. */

static uint8_t m_rx_buf[sizeof(TEST_STRING) + 5]; /**< RX buffer. */

static const uint8_t m_length = sizeof(m_tx_buf); /**< Transfer length. */

static volatile bool spis_xfer_done; /**< Flag used to indicate that SPIS instance completed the transfer. */

/**

* @brief SPIS user event handler.

*

* @param event

*/

void spis_event_handler(nrf_drv_spis_event_t event)

{

if (event.evt_type == NRF_DRV_SPIS_XFER_DONE)

{

spis_xfer_done = true;

NRF_LOG_INFO(" Transfer completed. Received: %s",(uint32_t)m_rx_buf);

}

}

int main(void)

{

// Enable the constant latency sub power mode to minimize the time it takes

// for the SPIS peripheral to become active after the CSN line is asserted

// (when the CPU is in sleep mode).

NRF_POWER->TASKS_CONSTLAT = 1;

bsp_board_init(BSP_INIT_LEDS);

APP_ERROR_CHECK(NRF_LOG_INIT(NULL));

NRF_LOG_DEFAULT_BACKENDS_INIT();

NRF_LOG_INFO("SPIS example");

nrf_drv_spis_config_t spis_config = NRF_DRV_SPIS_DEFAULT_CONFIG;

spis_config.csn_pin = APP_SPIS_CS_PIN;

spis_config.miso_pin = APP_SPIS_MISO_PIN;

spis_config.mosi_pin = APP_SPIS_MOSI_PIN;

spis_config.sck_pin = APP_SPIS_SCK_PIN;

spis_config.def = 0xaa;

// spis_config.orc = 0x55;

APP_ERROR_CHECK(nrf_drv_spis_init(&spis, &spis_config, spis_event_handler));

while (1)

{

memset(m_rx_buf, 0, m_length);

spis_xfer_done = false;

APP_ERROR_CHECK(nrf_drv_spis_buffers_set(&spis, m_tx_buf, m_length, m_rx_buf, m_length));

while (!spis_xfer_done)

{

__WFE();

}

NRF_LOG_FLUSH();

bsp_board_led_invert(BSP_BOARD_LED_0);

}

}

when i set the spi mode to mode1, mode2, it works。

when i set the spi mode to mode0, mode3, the error occurs。

I donot known why