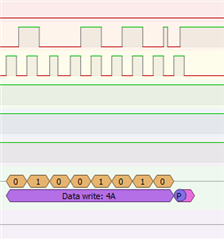

I am using TWI 0 to communicate with an external EEPROM. 99% of the time this is going succesfully. For reasons best known to itself, my eeprom will sometimes fail to acknowledge read requests properly, leaving the SDA line in an abnormal state.

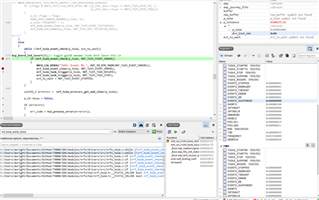

I can identify that this has happened via a timeout and would have been able to recover, but the TWI interface is hanging in while (!nrf_twim_event_check(p_twim, evt_to_wait)) within twim_xfer() from SDK 15.3.0

Rather than ensure my slave device never does anything unexpected, I'd prefer to make my code able to withstand these faults, simply providing back a read error.

Are there any recommended methods for adding a timeout within this loop or for clearing flags externally so that this loop breaks out with a fault instead of continuing to hang?