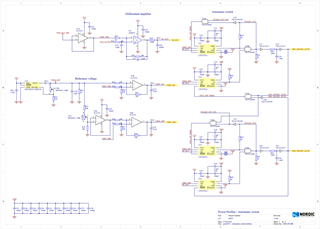

I'm trying to learn more about automatic current range switch and stumbled across Nordic's nRF6707 power profiler kit that has very interesting topology to choose between three different current ranges.

Now I "understand how" this circuit works but what I'm having hard time with is figuring out how to start analyzing thresholds, different start conditions and in general doing deeper analysis of this circuit in order to have proper understanding of how it works.

Here is the screenshot of the schematic portion for automatic switch:

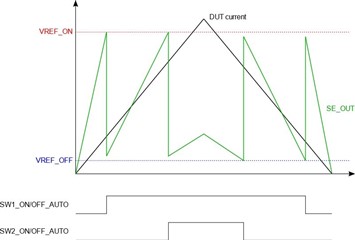

What I'm having trouble with and could really use help with, is suggestions on how to start analyzing automatic switch portion. I'm not sure how to find steady-state values and also initial conditions (although I assume both SW1 and SW2 should be off on power-up with no load) and also how to analyze transitions when measured current crosses Vref On/Off thresholds (in up or down direction).

Any help or suggestions would be much appreciated!