Is there any sample for spi based on nrf5340?

Is there any sample for spi based on nrf5340?

Hi.

There are no SPI samples that are created especially for the nRF5340.

However, both the spi_flash and spi_fujitsu_fram samples (in ncs/zephyr/samples/drivers) should work on the nRF5340 with a few modifications.

The spi_fujitsu_fram sample should work as long as an mb85rs64v is connected to SPI1.

The spi_flash sample will require you to add connect a flash chip that has a driver in Zephyr and add it to the device tree.

One of my colleagues has an SPI sample on his personal Github account: https://github.com/Rallare/fw-nrfconnect-nrf/tree/nrf9160_samples/samples/nrf9160/spi

While it was written for the nRF9160, it should work without any modifications on the nRF5340 (though the 53 might use different pins). Note that it has not been updated in a while, so it might not work on newer versions of NCS without some modifications.

Best regards,

Didrik

The spi_fujitsu_fram sample has the same problem。

Hi,Didrik

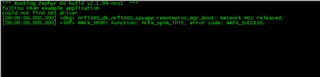

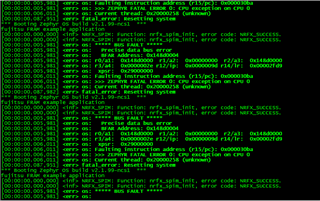

When I try to add spi0 to configuration, it always reports such an error.

Do you get another window before that?

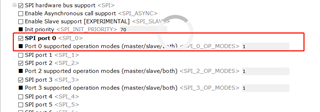

The problem is probably that UART0 is already used. As I said, they share the same peripheral on the nRF53, so only one of UART0, SPI0, and TWI0 can be enabled at the same time.

You also probably have to enable the SPI node in the device tree.

Yes, UART0 enabled for log

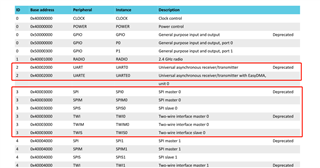

But UART0 and SPI0 seem to be different instantiations

I change SPI0 to SPI1,the configuration passed,and log changed.

Hi.

sean said:But UART0 and SPI0 seem to be different instantiations

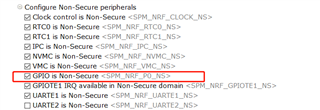

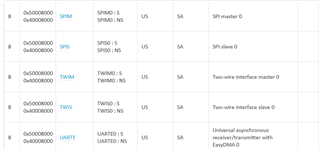

Are you certain that you are looking at the right datasheet? For me, they are the same:

I have been able to port my colleague's sample to nrf5340_dk_nrf5340_cpuappns (notice the "ns" at the end. The sample only builds for the non-secure version of the board).

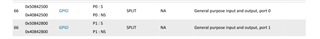

As you can see from the overlay file, pins 4,5 and 6 are used by SPI_1. If you connect pins 4 & 5, you will see the sent value being looped back.

You can find the modified sample attached (I left the compiled hex file).

Best regards,

Didrik

Hi, Didrik

Thanks very much! It works.

Sorry,I mix with 52840's datasheet.

And at first, in nrf5340_dk_nrf5340_cpuappns configuration,I download zephyr.hex,it didn't log any thing,so I allways use nrf5340_dk_nrf5340_cpuapp configuration.

Thanks again!

Hi, Didrik

Thanks very much! It works.

Sorry,I mix with 52840's datasheet.

And at first, in nrf5340_dk_nrf5340_cpuappns configuration,I download zephyr.hex,it didn't log any thing,so I allways use nrf5340_dk_nrf5340_cpuapp configuration.

Thanks again!

sean said:And at first, in nrf5340_dk_nrf5340_cpuappns configuration,I download zephyr.hex,it didn't log any thing,so I allways use nrf5340_dk_nrf5340_cpuapp configuration.

For the non-secure configuration, you need to use merged.hex. When the application is running as non-secure, it needs another "application" to set up the CPU and peripherals first, such as the Secure Partition Manager (SPM).

When building your application as non-secure, the SPM sample gets built automatically, and the hex files are merged into "merged.hex".

I've added some links to the relevant documentation below:

https://developer.nordicsemi.com/nRF_Connect_SDK/doc/1.2.0/nrf/samples/nrf9160/spm/README.html

https://developer.nordicsemi.com/nRF_Connect_SDK/doc/1.2.0/nrf/include/spm.html

https://developer.nordicsemi.com/nRF_Connect_SDK/doc/1.2.0/nrf/ug_multi_image.html

Hi, Didrik

I can control GPIO P0,but can't control P1, when I load project with nrf5340_dk_nrf5340_cpuappns configuration.

If I load project with nrf5340_dk_nrf5340_cpuapp configuration, I can control both P0 and P1.

Why there is no P1 in nrf5340_dk_nrf5340_cpuappns spm configuration?