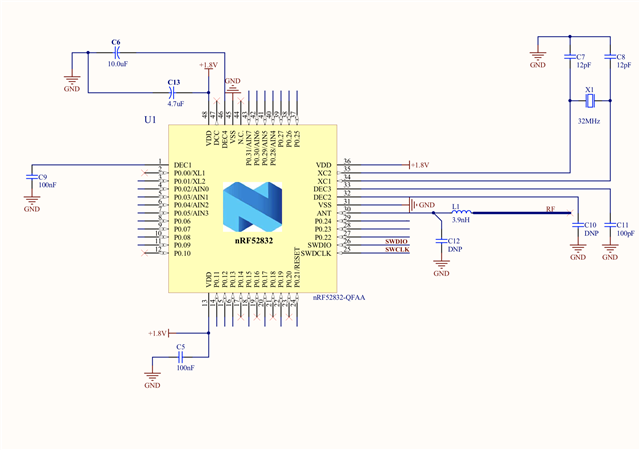

We recently ported to the nRF52832 and our electrical engineer had to make a couple changes from the reference design due to space constraints. The port has worked well during internal testing but unfortunately a unit running the standard DTM firmware died on the company that is testing it for CE Marking. The testing company is using nRFgo Studio with our unit being powered by UART and a lipo battery. They said it worked correctly for one day of testing and then the next day it wouldn't power up.

We have since run a lot of tests internally on multiple units with the DTM firmware controlled by nRFgo Studio and unfortunately have not been able to recreate the issue. The testing company thinks the issue could be caused by our deviation from the reference design, specifically the changes on the capacitors on VDD.

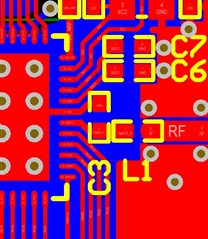

I've included our schematic and layout below. Could our minor deviations from the reference design cause the nRF to die during DTM testing? What (if any) issues would you expect these changes from the reference design to cause? Please let me know if any additional information will help. Thanks for any input!