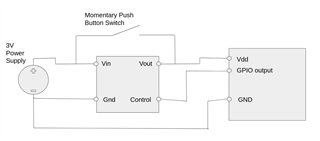

Hello, I am building a power switch for my application and have some questions about expected behavior when holding a GPIO output signal at HIGH during System ON sleep mode. Briefly, I want to use the TCK106AG load switch IC (TCK106AG) with a tactile switch across the Vin and Vout pins. When a power supply is first attached to the system, the nRF52810 I am using will remain off. When the tactile switch is pressed, the first instruction in main() will be to turn a GPIO output pin to HIGH state, connected to the control pin on the TCK106AG, and hold this HIGH state. This way, when the momentary tactile switch is released, the nRF52810 will remain on as the TCK106AG will deliver voltage to the nRF52810 as long as Control pin is held HIGH. See the attached image to see the circuit.

Briefly my entire application works as follows: Power on, read sensor data, advertise/connect to smartphone, transmit sensor data, enter low power System ON sleep mode, repeat. The device will remain in system ON sleep mode for 15 minutes between reading and transmitting sensor data. The application needs to consume as little current as possible to maximize battery life. If I use the TCK106AG load switch IC, and hold a GPIO output at a HIGH state, how much current will be drawn during System ON sleep mode? I mean only current drawn from the GPIO pin due to holding a HIGH state, not the entire application.

I have another potential solution which uses two MOSFETs (n-fet and a p-fet) with a tactile switch such that sending a constant LOW signal to the n-fet will allow voltage to be provided to the nRF52810 and keep it powered on. In this solution, I would hold a constant LOW signal from the GPIO output pin. Would there be any difference in current draw from the GPIO output pin between these two solutions (TCK106AG with constant GPIO HIGH vs. dual mosfet with constant GPIO LOW)?

I mainly write software and do not have as much expertise with electronics like this. From my basic understanding, if GPIO state is held LOW then with Ohm's law you'd have 0V = (current) * (resistance), so given any resistance at the n-fet gate 0 current would be drawn. However, if GPIO state is held HIGH then you'd have 3.3V = (current) * (resistance) and you'd definitely have at least some current draw. Even if resistance is 10 megaohms, this would be approximately 0.33 microampere draw. Our application is extremely, extremely low power so an additional 0.33 microampere draw during sleep mode would not be acceptable.

Any insight or help on this current draw question would be greatly appreciated, thank you very much!