Hi, I have a few questions about the SPI master module. I'm using it for an application that basically needs to be gapless. After quite a bit of work, I've gotten it to work full speed at 4MHz with no gaps (outside of an ISR). However, I had to do a few...undocumented things. In particular, it was necessary for me to switch the order of clearing the EVENT_READY flag, reading RX, and writing TX. In the example code, the order is EVENT_READY, RX, then TX, but when I change it around in my code (mainly for TX to be earlier) I can achieve continuous, gapless SPI transmission at 4MHz.

From what I'm guessing from observed behavior, there is an undocumented requirement for TX to be buffered at least (about) 4 SPI clock cycles before it comes up on the queue (or 1us). My optimized code seems to need just 2-4 cycles to achieve that requirement (reliably while waiting for EVENT_READY), so I need that TX to come earlier. Can this program order be reliably supported? I haven't observed any unexpected behavior yet. I'm assuming there's someone familiar with the internal SPI state machine who could comment on whether or not this might be unreliable in some situations. Otherwise I'm going to have to set up a testbench and everything to determine if we'll be able to achieve our required performance with the 51822 in production.

I also read somewhere that 8MHz operation can be set, but isn't reliable. Is this because it's impossible to write a loop on the Cortex-M0 that'll feed data and check flags fast enough? Is this still true for newer revision chips? (I'm using a G0 device IIRC, but I'd imagine I'll have a newer device for production).

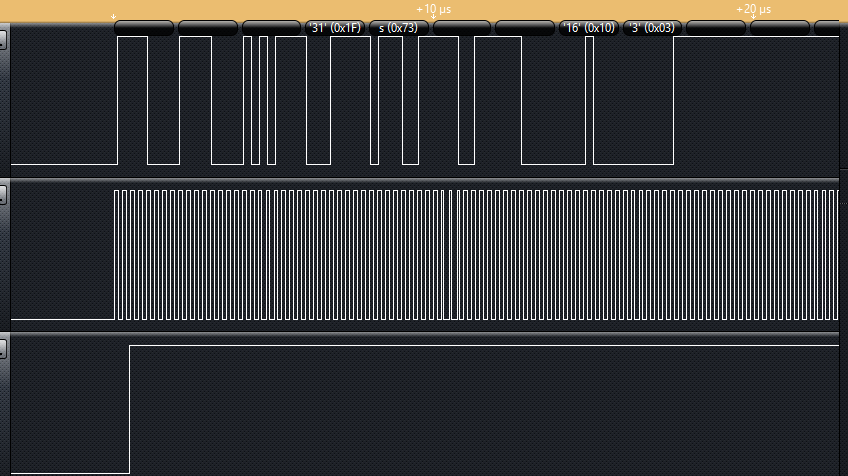

There's some weird short/long pulses in the logic analyzer capture below, but I suspect that's just clock phase mismatch between the analyzer / nRF51822. It's for most intents and purposes gapless.