Hi,

Can we give a voltage more than VDD+0.3V on an open drain high impedance configured IO pin? By open drain, I mean:

nrf_gpio_cfg(pin_num, NRF_GPIO_PIN_DIR_OUTPUT,

NRF_GPIO_PIN_INPUT_DISCONNECT,

NRF_GPIO_PIN_NOPULL,

GPIO_PIN_CNF_DRIVE_S0D1,

NRF_GPIO_PIN_NOSENSE );

Since its an open configuration, can it still damage the controller?

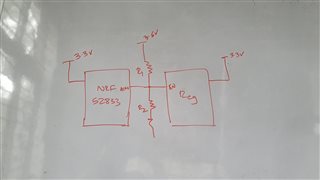

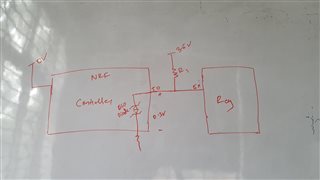

Due to a design error, we are getting 3.6V on an IO pin whereas the NRF VDD is at 2.5V.

We will fix this design error for future productions but for the current produced boards (which is quite a lot), I am wondering if the above workaround can be done.

Or is there any other pin configuration which can mitigate this damage?

Thank you,

Chethan