Hi

Hi

nRF52840 SWD is push pull or open drain type?

And we want add level shifter between J-Link and nRF52840, do you have recommend level shifter PN? Or what type of level shifter we need select(no internal pull, etc..)

Thank you~~

Poki

Hi

Hi

nRF52840 SWD is push pull or open drain type?

And we want add level shifter between J-Link and nRF52840, do you have recommend level shifter PN? Or what type of level shifter we need select(no internal pull, etc..)

Thank you~~

Poki

level shifter between J-Link

Why? Commercial J-Links have level shifters included - that is why you need V_TRef connected to VCC on the NRF chip.

Hi Turbo:

Because we found when connect to J-Link, when we download image, measure V_TRef voltage is VDD(we provide 2.1V to nRF VDD), this is ok. But when not download image, the V_TRef become 2.85V, and we disconnect J-Link and nRF, measure V_TRef is 3V, seems when not download image, the V_TRef will not follow VDD. We afraid this will damage our PMIC, so want add level shifter.

Hi Turbo:

Because we found when connect to J-Link, when we download image, measure V_TRef voltage is VDD(we provide 2.1V to nRF VDD), this is ok. But when not download image, the V_TRef become 2.85V, and we disconnect J-Link and nRF, measure V_TRef is 3V, seems when not download image, the V_TRef will not follow VDD. We afraid this will damage our PMIC, so want add level shifter.

Is this on a custom board or on a nRF52840 DK? Are you using the on-board debugger of a DK, or do you use an external J-Link device (if so, which one)? Can you post the schematics showing how the debugger is connected to the nRF/board?

Hi Jorgen:

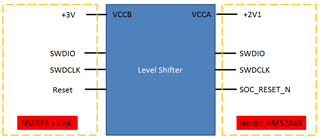

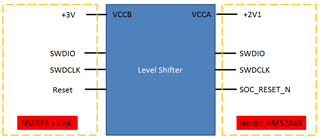

It is custom board not DK, we use external J-Line device(segger J-Link, https://goods.ruten.com.tw/item/show?21311175219003)

And we directly connect 2V1, SWDIO, SWDCLK, SOC_RESET to segger J-Link.

Poki

If you are using a standalone Segger J-Link debugger and its V_TRef is higher than expected when not downloading/debugging the chip, you will have to check this with Segger support.