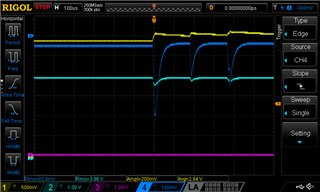

Vdd generated from Vddh is unstable without connected debugger and with non-started soft device

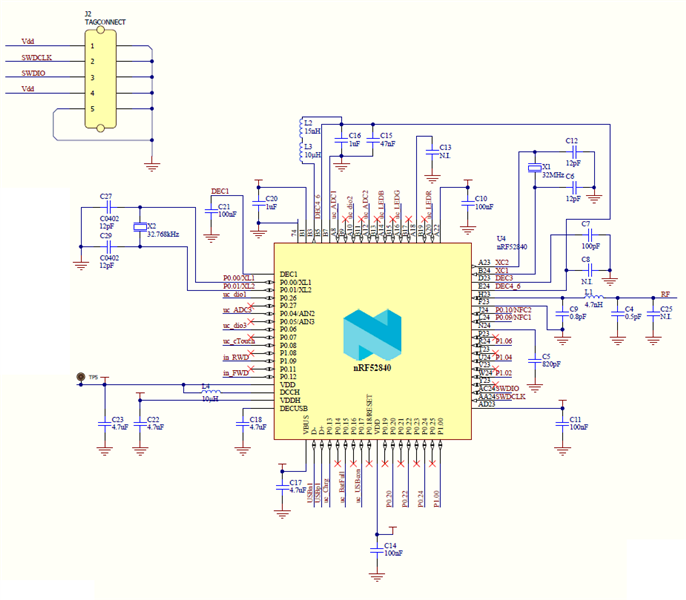

We are developing a battery powered device based on nRF52840 on custom PCB. We are aiming to use nRF52840 DCDC REG0 to provide 3V Vdd from Li-ion battery. Vdd would also be used to run some peripherals but the current should be below 25 mA. Firmware was developed on nRF52 DK and successfully ported to custom board. With exception of unstable Vdd.

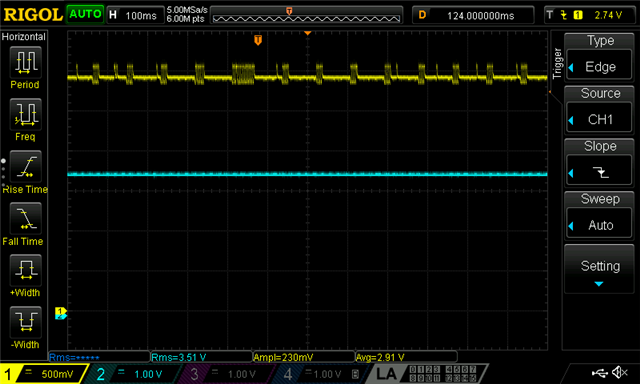

The circuit is made based on the circuit configuration no. 4 from nRF52840 datasheet v 1.1 p591. Inductors L2, L3 and capacitors C15 and C16 are in place. Also all other capacitors and inductors). Vdd is stable when the debugger (nRF52 DK) is connected. REG0 DCDC converter (and REG1 also) is enabled between initialize() and start() function in main (based on mesh light server example).

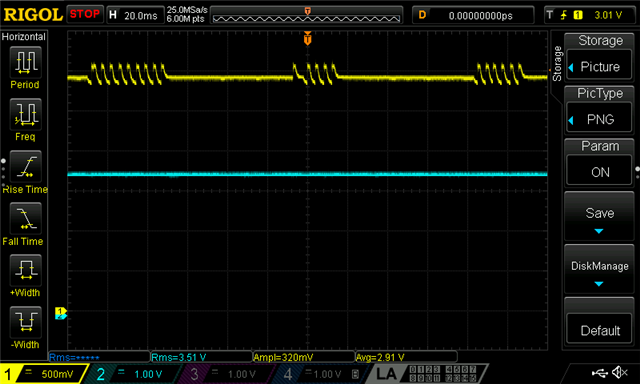

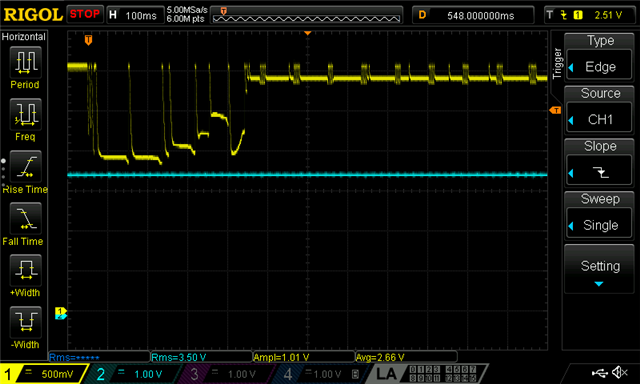

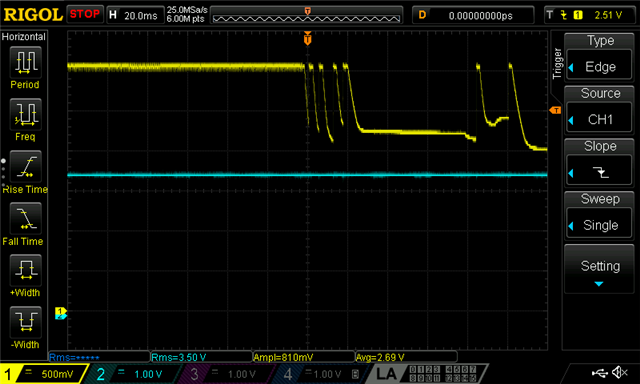

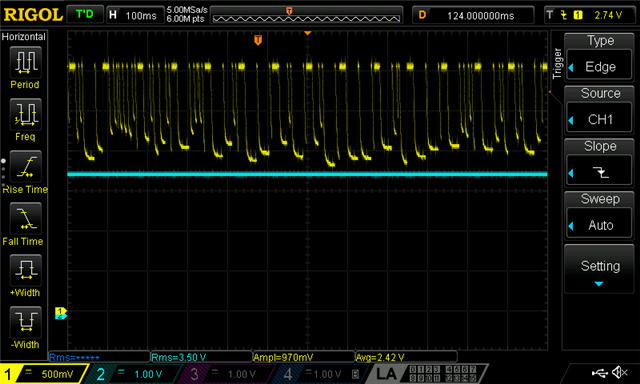

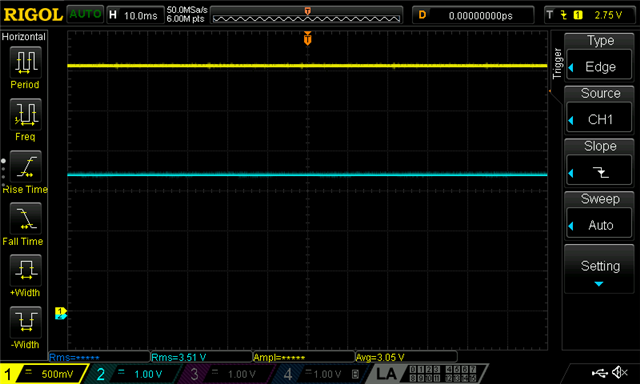

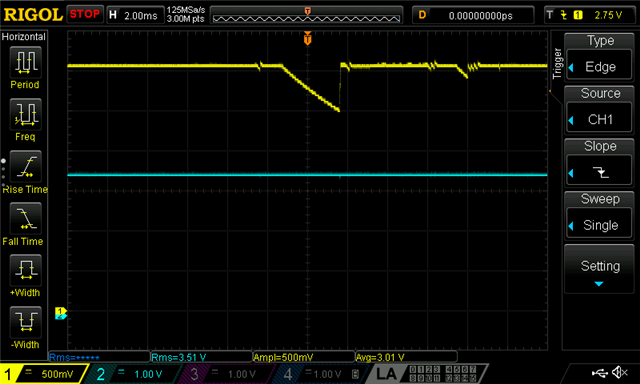

As long as I program the CPU with the debugger and then reset it via SWDebug the Vdd is stable. Even if I disconnect the debugger, the circuit stays stable. As soon as I start the circuit by connecting it to external supply (the same as used previously for programming) Vdd becomes unstable.

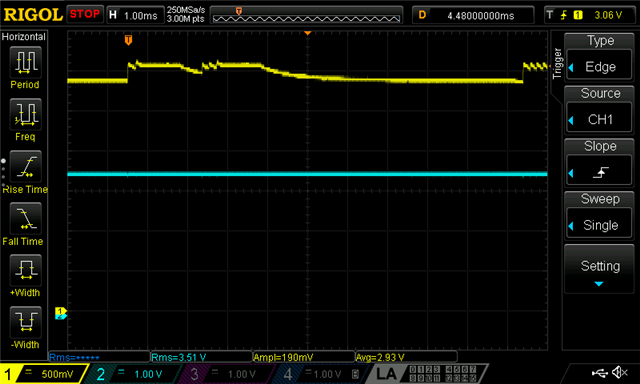

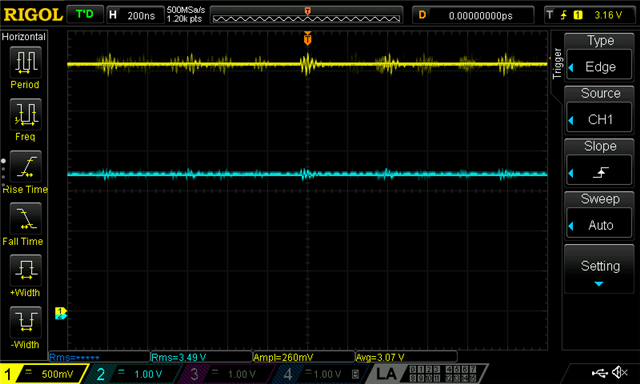

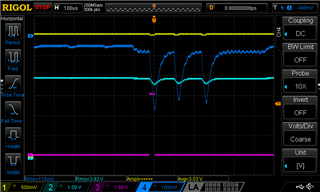

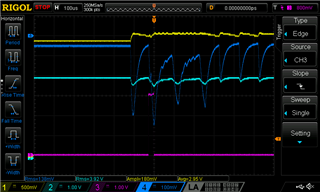

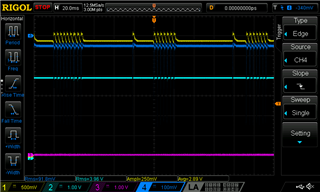

For debugging purposes I did not start the soft device while experimenting. After two days of debugging several sub circuits and playing with blocking capacitors, I checked the code again and out of desperation (and function name: sd_power_dcdc0_mode_set(NRF_POWER_DCDC_ENABLE);) enabled the soft device (just before writing to forum) and the Vdd stayed stable even if the circuit was started by connecting external supply only without debugger.

This seems like a very odd bug (or I missed some warnings somewhere).

My question now is, whether this behavior is expected? It seems very strange.

Thank you!