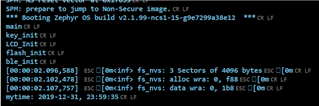

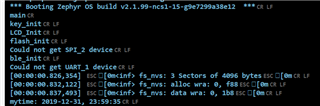

My project has successfully debugged the communication of SPI_2, SPI_3 and UART_1. Now I need to debug the interface communication of I2C, when I turn on the macro switch related to I2C, it can't get binding of SPI_ 2 and UART_ 1. What is the reason?

my prj.conf file is like this:

# # Copyright (c) 2019 Nordic Semiconductor ASA # # SPDX-License-Identifier: LicenseRef-BSD-5-Clause-Nordic # # General config CONFIG_TRUSTED_EXECUTION_NONSECURE=y CONFIG_NEWLIB_LIBC=y CONFIG_ASSERT=y CONFIG_REBOOT=y CONFIG_GPIO=y CONFIG_LOG=y CONFIG_LOG_IMMEDIATE=y # Network CONFIG_NETWORKING=y CONFIG_NET_NATIVE=n CONFIG_NET_SOCKETS=y CONFIG_NET_SOCKETS_OFFLOAD=y # Modem info CONFIG_MODEM_INFO=y # BSD library CONFIG_BSD_LIBRARY=y CONFIG_BSD_LIBRARY_TRACE_ENABLED=n # Library for buttons and LEDs CONFIG_DK_LIBRARY=y CONFIG_DK_LIBRARY_INVERT_LEDS=n # Heap and stacks CONFIG_HEAP_MEM_POOL_SIZE=16384 CONFIG_MAIN_STACK_SIZE=8192 CONFIG_SYSTEM_WORKQUEUE_STACK_SIZE=2048 CONFIG_HW_STACK_PROTECTION=y # MCUBOOT CONFIG_BOOTLOADER_MCUBOOT=y CONFIG_IMG_MANAGER=y CONFIG_MCUBOOT_IMG_MANAGER=y # SPI CONFIG_SPI=y CONFIG_SPI_NRFX=y CONFIG_SPI_2=y CONFIG_SPI_2_NRF_SPIM=y CONFIG_SPI_3=y CONFIG_SPI_3_NRF_SPIM=y # I2C #CONFIG_I2C=y #CONFIG_I2C_NRFX=y #CONFIG_I2C_1=y #CONFIG_I2C_1_NRF_TWIM=y #CONFIG_I2C_INIT_PRIORITY=60 # Flash CONFIG_FLASH=y CONFIG_IMG_ERASE_PROGRESSIVELY=y # NVS CONFIG_FLASH=y CONFIG_FLASH_PAGE_LAYOUT=y CONFIG_NVS=y CONFIG_LOG=y CONFIG_NVS_LOG_LEVEL_DBG=y CONFIG_REBOOT=y CONFIG_MPU_ALLOW_FLASH_WRITE=y # UART CONFIG_SERIAL=y CONFIG_UART_INTERRUPT_DRIVEN=y CONFIG_UART_LINE_CTRL=y #CONFIG_UART_0_NRF_UARTE=y #CONFIG_UART_0_NRF_FLOW_CONTROL=n CONFIG_UART_1_NRF_UARTE=y CONFIG_UART_1_NRF_FLOW_CONTROL=n # Use smaller buffers for net_buf as CANBUS packets are quite small. CONFIG_NET_BUF_DATA_SIZE=64 CONFIG_NET_BUF_USER_DATA_SIZE=1