Hi

I'm currently trying to use a cheap stlinkv2 clone flashed with https://github.com/x893/CMSIS-DAP for at test setup.

(cmsis-dap enables it to remove APPROTECT/read back protection)

It works fine (currently only at half the speed of a "JLink Base"), but I would also like to be able to reset the chip to have the debug interface disabled.

For the nRF51 I have seen a description of a way to reset the chip:

https://devzone.nordicsemi.com/f/nordic-q-a/11/why-does-my-nrf51822-consume-1-ma-in-sleep

But as the nRF52 is different in this regard that method can't be applied.

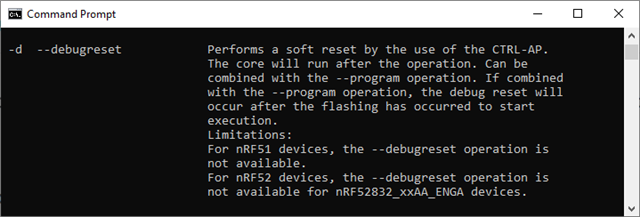

As "nrfjprog -p --family nrf52" using a J-Link works (if done before a soft reboot which enables APPROTECT)

I know that it is possible to somehow reset the chip deep enough, that the debug interface is disabled using only SWDIO and SWDCLK.

So my question is: How does "nrfjprog -p --family nrf52" reset the chip?

Kind regards Visti Andresen