These questions are in the context of using an nRF52840 in a serialization application. But I don't believe this will impact the information I am trying to understand. The following questions are in the context of using an nRF52840 for both the application and connectivity process. However, the customer's end product will use a 3rd party MCU fr the application processor.

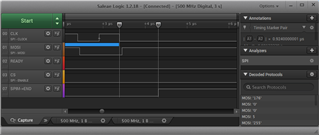

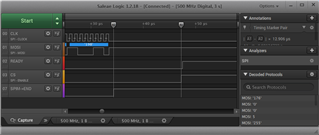

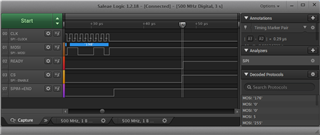

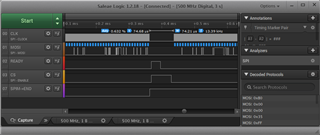

Referring SPI RAW - packet writing, I have been asked what causes the approximate 10 uS delay from the end of the 2nd byte to /RDY transitioning to a high state. I assume this is simply overhead in the Slave or Master driver. What is bugging me is I am unable to determine is /RDY is responding to the /CD transition or an independent event with the slave.

Where can I find the timing information for SPIM NCS? I would expect to see something similar information provided for the SPIS in section 6.26.6.2. Specifically, what is the timing from when the last bit is transmitted until CSN is deselected?

I think I understand the Slave's RDY transition in response to SPI_RAW_STATE_RX_HEADER or SPI_RAW_STATE_RX_PAYLOAD. But it's not clear is this because the buffer is filled if this the result NCS being deasserted. Please advise.

Can you provide a more detailed understanding of what causes the is 10 uS delay10 uS delay from the end of the 2nd byte to /RDY transitioning to a high state.

The customer payloads will vary in size and some will exceed 255 bytes. Can you point me to a reference as to how CS and RDY would or would not transition during a 770-byte data payload. To use the sterilization application, I assume that the application would imagine sending packets of 255 - 255- 255 - 5 in separate transactions? And CS and RDY would have the same timing as the SPI RAW - packet writing timing diagrams. But if one wrote an independent application, where the gold was to send one block of 770 bytes I suspect that CS will remain active for the whole transaction and READY would remain asserted as long as there is enough memory to store the receive data?

Thanks,

Jeff