We use our own board with both nRF52840 and nRF9160. We run into a problem trying to implement a circuit that enables the nRF9160 to reset the nRF52840. Things work fine if we disable the pinreset in nRF52840.

Background:

- We start the nRF52840 first. It is powered with 1.8V.

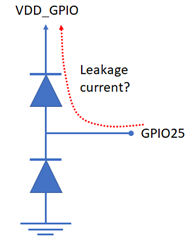

- The nRF9160 has VDD (3.0V - 4.2V in this case) supplied. The ENABLE pin of the nRF9160 is pulled down at the start (nRF52840 enables it when needed). VDD_GPIO is not supplied when ENABLE is down.

- The device tested uses an NRF9160-SICA-B1A sample - but it seemed that the same behaviour exists in NRF9160-SICA-B0A

Problem: The P0.25 pin of the nRF9160 is connected to the nRESET of the nRF52840. If we enable the pinreset configuration in UICR, the internal pull-up of the nRF52840 fails to pull the pin high, the voltage raises to 0.93V - 1.05V only. It seems like the nRF9160 pulls the pin down. If the ENABLE pin of the nRF9160 is raised and VDD_GPIO supplied, the nRF9160 P0.25 goes to high-Z state and the nRF52840 pinreset pullup pulls the pin to 1.8V. It seemed that pulling ENABLE down after this leaves the reset line at 1.8V. Our system does not boot if the pinreset is enabled as the nRESET voltage is too low and the nRF52840 remains in the reset state.

I did not find this nRF9160 behavior documented anywhere. Is this the correct interpretation? Is there any difference if we switched to another pin in nRF9160? (The P0.25 has also TRACE3 function - seems unlikely but possible that it could interfere). Is there some workaround for this that would allow the nRF9160 GPIO pin to be connected to the nRESET of the nRF52840 - when nRF9160 ENABLE is kept low at boot?

Adding a pullup resistor would help to raise the voltage but it raises the current consumption way too much.

Pertti