I don't fully understand datasheet for LFXO.

17.4.3

CL_LFXO Load Capacitance = 12.5pF. Is this the recommended CL for external crystal?

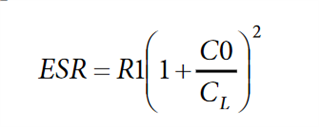

RS_LXFO ESR = 100k. Is this the max ESR in crystal OR is this a ESR on the chip?

PD_LFXO = 1uW. Is this the recommended minimum Drive Level for crystal OR is this max outout power to crystal?

ILFXO = 0.23uA. Is this the current for silicon driving the crystal or is this the max output current to crystal?

I must be sure to not "overdrive" crystal. The crystals Drive Level I'm thinking of can be 0.1uW.

Kan anybody enlighten me because the datasheet it's not obvious to me.