I'm currently working on the nrf52832_qfax_dcdc pcb after adding a few components. I need to route to pins p0.22, p0.23 SWDIO and SWDCLK but am unable to route away from the original layout. For reference:

The red square surrounding the nrf52832 just represents a GND copper plate I'm assuming. And when I try to route off of this red square area I'm unable to do this. I see the other parts that route over it have gaps in the red square area, but I wasn't sure how to modify this to route off of the area. Any help with this issue or general advice would be greatly appreciated, thanks!

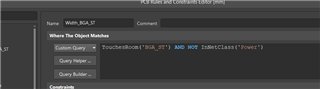

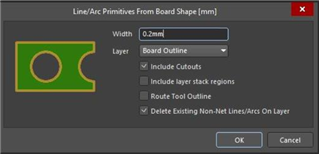

Update: There seems to be a clearance boundary surrounding the square as shown below that is stopping me from routing to the 52832. Is there a way to alter this so that I can route past this? The same boundary also exists on the bottom layer as well. I've realized this comes from the keepout layer, and was wondering if it was okay to remove it so that I can route to the 52832. I assume it is there for a reason but I'm not sure how else to route to the chip.