Hello

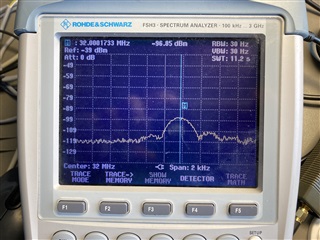

The Uart Baudrate is initiliazed at 115200 baud but i the BLE nRF52833 is sending with about 115900.

I try to switch to hf clock but the baudrate is to high.

// Request and wait for it to be ready.

err_code = sd_clock_hfclk_request();

APP_ERROR_CHECK(err_code);

uint32_t hfclk_is_running = 0;

while (!hfclk_is_running)

{

APP_ERROR_CHECK(sd_clock_hfclk_is_running(&hfclk_is_running) );

}

Hello Marjeris

Hello Marjeris