Hello,

we are currently experiencing issues with the SPI interface which we suspect is due to the behaviour of the MOSI line in idle state. We have noticed that during communication the last byte of a message decides at which level the MOSI line will stay in the next idle cycle (not affected by ORC). From what we have seen so far a leading 1 of the last byte (>=0x80) leads to the MOSI line staying HIGH whilst a leading 0 (<0x80) leads to an idle LOW state.

We suspect that due to this behaviour our SPI connected device crashes when a special command is triggered. To be more precise: If MOSI idle state switches during a sequence of messages out SPI device crashes and we have to reset our system.

This issue seems closely related to: https://devzone.nordicsemi.com/f/nordic-q-a/41266/nrf52832-why-does-mosi-stay-high-after-transmitting-any-byte-7f and https://devzone.nordicsemi.com/f/nordic-q-a/77430/why-does-mosi-stay-high-afther-sending-last-byte-with-a-value-higher-than-decimal-127-binear-0111-1111

I assume that this issue is still present. Is there maybe a way we can force MOSI into a defined state to check if that is really the issue at hand? We have tried adding a pull-up/pull-down resistor but MOSI seems to be actively driven to a certain state. We have also tried using SPI_0 through to SPI_3 without any success. All of them show this kind of behaviour.

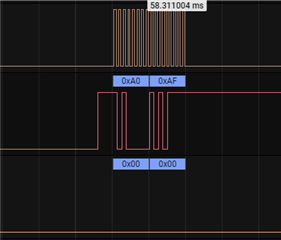

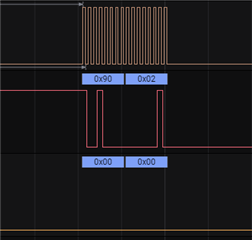

To visualize the issue at hand here are a couple examples:

MOSI ending with 0xAF leads to a HIGH idle state.

MOSI ending with 0x02 leads to a LOW idle state