Hello,

We are attempting to track down a rare bug in our code that causes the device to occasionally hard fault.

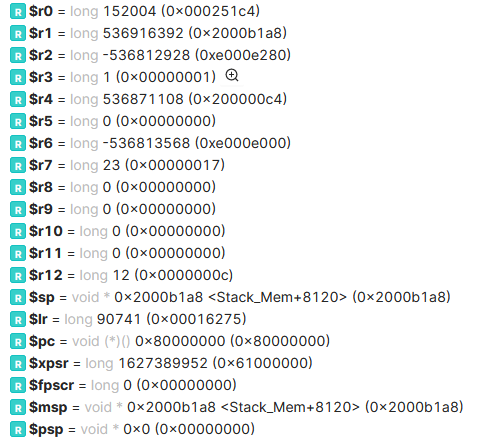

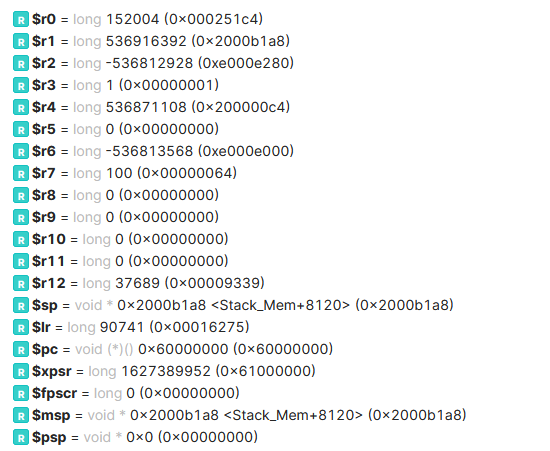

We have been able to catch it three times, twice where it attempted to execute an instruction at 0x80000000 and once at 0x60000000.

The state of the device is almost the same for all cases, with the working registers having the same values except R12 and R7.

Even the link register is the same for both with a return destination of 0x00016275.

Since the program is executing in the soft device region, could someone look to see what is happening in and around that region?

I am hoping it might give us some more insight into why these hard faults happen.

I checked and our application stack hasn't overflown.

Otherwise any insights or points of direction would be appreciated.

Thanks,

James

(Instruction Fault at 0x80000000) (Instruction Fault at 0x60000000)