Hello,

I'm using the flash MX25L1283 together with the NRF52840. I've implemented a new driver for that flash using the nrfx library. Everything works fine !

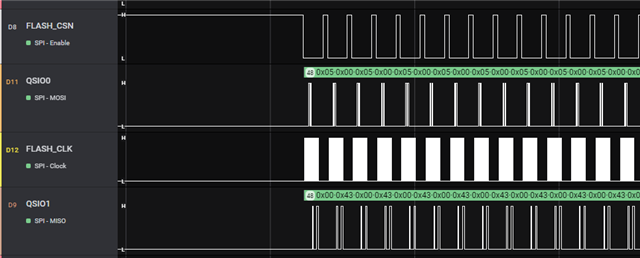

However, I can't understand what's the EVENT_READY. When nrfx_qspi_init() is called, it seems that the external flash will be accessed to read the "Write in progess" bit ? This is done in a loop until that bit is cleared, right ? I can see a lot of 0x05 command (read status register) executed there.

When exactly that read status register is done ? When we send a custom command with "WIP_WAIT" flag setted, we will read that status register before sending the command, right? Is the status register read after that or not at all ? I can see that you are also waiting for the EVENT_READY there.

Thanks in advance for your reply

Best regards

Rémy