Hi Nordic community

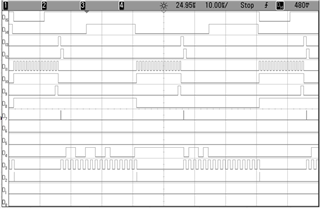

We have a custom IC to interface with the nRF52840 chip. We did testing for that IC with FPGA and the related control, clock signals are as shown in the figure below. The frequency of these signals when interfacing with nRF52840 will be slower, with the highest frequency of 1 MHz.

It's not too hard to generate these signals with precise timing controls in FPGA but I'm wondering if this is doable with nRF52840? And would you recommend a good strategy to do it (nRF5 SDK or nRF Connect SDK are both fine for us)?

Thanks,

Richard