Hi Team,

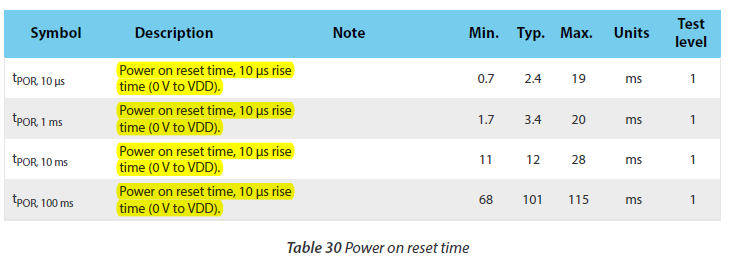

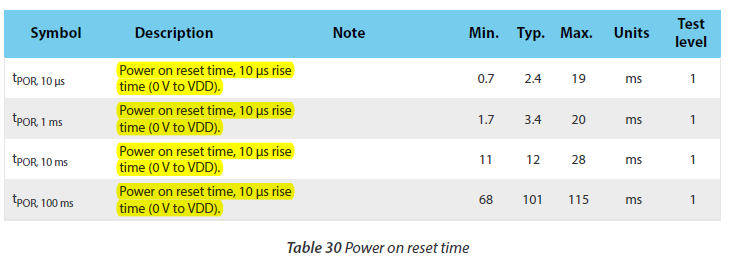

about power on reset time, not very clear about the description in the SP3.1 as in the attached picture,

why the description are the same?

what's the difference between tPOR,10us / tPOR,1ms /tPOR,10ms /tPOR,100ms

why the description are the same?

what's the difference between tPOR,10us / tPOR,1ms /tPOR,10ms /tPOR,100ms

thanks, vincent

Hi Team,

about power on reset time, not very clear about the description in the SP3.1 as in the attached picture,

why the description are the same?

what's the difference between tPOR,10us / tPOR,1ms /tPOR,10ms /tPOR,100ms

why the description are the same?

what's the difference between tPOR,10us / tPOR,1ms /tPOR,10ms /tPOR,100ms

thanks, vincent

Hi. This is a documentation error. I it should say 10us, 1ms, 10ms and 100ms in the descriptions as well. It is reported to our technical writers. Thank you for bringing it to our attention.

EDIT:

The reason why t_POR is longer than the rise time, e.g. with 10us rise time t_POR is 2.4ms, is that the nRF51's internal voltage regulators need some time to stabilize before the CPU is allowed to read from flash.

Hi, thanks,

thanks, vincent