I am trying to implement spi in my project and have encountered an issue where the delay from chipselect to sclk is around 10 us which should be as low as 1us according to the nrf5340 datasheet and the slave device I am communicating with can have this time as low as 50ns.

I tried using both zephyr and nrfx drivers but saw the same issue. With nrfx I was able to reduce it to ~5us but not more than that. For nrfx driver I used a sample implementation directly without any modifications to be certain that I am not doing anything weird in my code base.

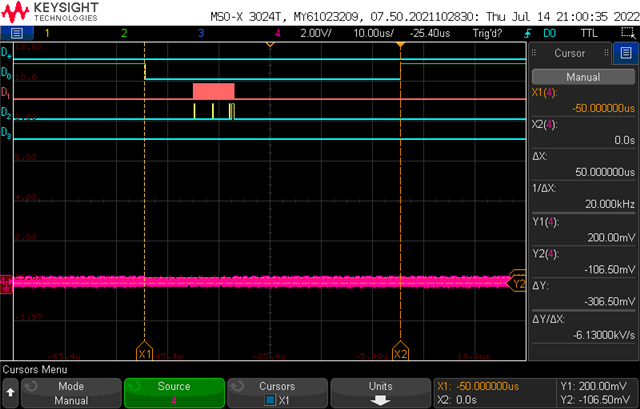

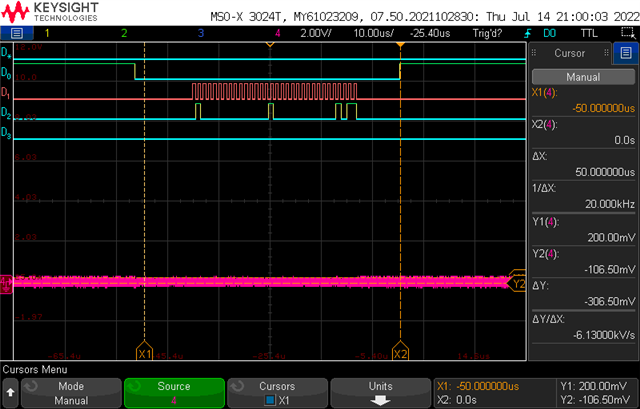

I have attached below scope pics for 1MHz and 4MHz where you can see that the freq does change but the setup time (cs to clk) at the start and end of payload does not change and therefore no difference in the time it takes to transfer the entire payload which is very odd as if this is the case then running at higher or lower frequency does not matter at all.

So is there any particular register I can use to control these delay times between cs and clk in start and end of the payload?

I also tried to go with bitbanging instead but could not get the clock to go faster than 2MHz. Can you please suggest how I can increase my freq to 4MHz if I want to go with this approach?