I am trying to use a SPI bus with three MAX3109 chips attached to give me 6 UARTS. My overlay is defined as follows:

I am trying to use a SPI bus with three MAX3109 chips attached to give me 6 UARTS. My overlay is defined as follows:

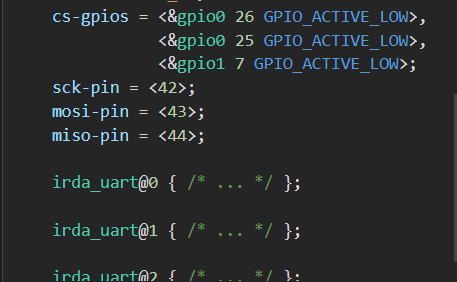

One thing I noticed - when I hover over the &spi1 in my overlay file to expand its contents, I see that it has added the cs-gpios information and pin assignments from the overlay. But the irda_uart nodes are showing that content automatically commented out. It seems that everything I define in there is being discarded, yet I'm not getting errors or warnings. See below.

Hi,

Could you provide zephyr.dts file which is located in <your_application_folder>\build\zephyr?

Could you please provide more information about "spi-device" that is present in your overlay file?

Best regards,

Dejan

Hi. I was able to make this work by changing the declaration of the spi_config struct a bit to just directly use the device tree macro SPI_CS_CONTROL_PTR_DT(). So I do the following:

Hi,

jmilliken said:it might be worth mentioning that the delay time specified in the macro is completely ignored.

Which macro do you refer to?

jmilliken said:Regardless of what I put there - I've tried values from 1 to 10 - the timing on chip select is always the same.

Could you please show where and how you specify delay values?

Best regards,

Dejan

Hi. I am referring to the macro SPI_CS_CONTROL_PTR_DT(DT_NODELABEL(irda_uart1), 2). Jumping to the definition of the macro gives me the following: