Hi,

Do you have a recommended circuit for supplying VDD_GPIO with the right timing relationship to VDD?

Section 11.1 of the datasheet says "VDD_GPIO should be applied after VDD has been supplied" and "VDD_GPIO should be removed before removing VDD".

I'm working on a PCB with a relatively simple power supply. Do I have to add load switches and timing logic to properly power up the nRF9160?

Thanks,

Børge

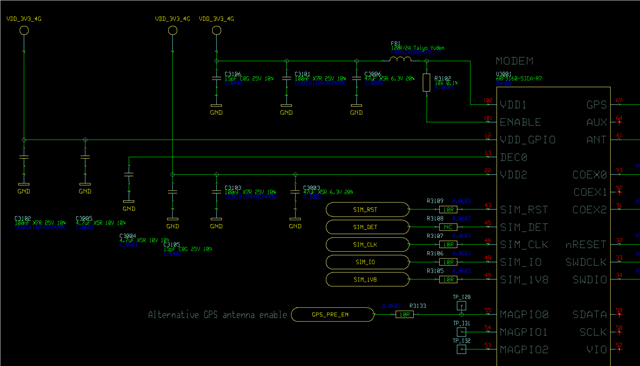

This is what the power section looks like at the moment. VDD_3V3_4G comes from a simple buck-boost converter and a Li-Ion battery.