Hi,

we have created a new product prototype where audio streaming is the functionality. 2 different HW revisions were so far built, the software originally is built to use a PDM to I2S converter chip, but now we had a chance to investigate the direct recording from the PDM microphones. The format we are using is 48Khz sampling 16bit stereo. This is working perfectly on I2S. However we have noticed weird behavior on the direct PDM recording.

We managed to create the code to use the microphones, the limitations be:

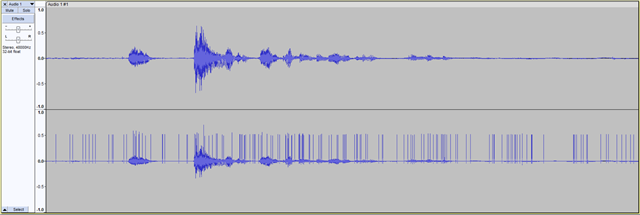

PDM clock is at 3.072 MHz (as 64X @ 48K) and ACLK clock source at 12.288 MHz. This yields the proper sampling speed. However it seems that the rising edge of the clock is glitchy at random intervals (we can't identify whether this means 0 samples or some other bit errors, the glitch repeat at around 100ms intervals sounds like static clicking with varied amplitude). We have tested 3 boards and swapped the microphones from left to right to check that it is not the routing on the pcb or the microphones. Glitch stayed always on the rising clock edge. We even tried different IO voltages to rule that out as well 1.8V and 2.3V were tried.

Interestingly the falling edge sampling of the clock works perfectly. (we have muted the other channel to see).

What worked but not usable for us:

- change PDM clock source to 32MHz but this yields sampling rate of 50kHz

- change sampling rate to 24kHz -> this yielded 1.536MHz PDM clock and that ran again fine with the 12.288MHz ACLK source.

So it seems that the glitch exists only on that one specific frequency (that we need of course). Our codec only allows 48/24/16/12/8 kHz sampling, so we can't try the 44.1kHz related frequencies.

Is there any known issues around this ACLK being 12.288MHz, and PDM clock at 3.072 MHz? Why does it only affect the rising clock edge? Is there anything we can do to make it work, or our best option is to go with the working speed of 24kHz audio sampling and 1.536MHz PDM clock?

Thank you

Levente

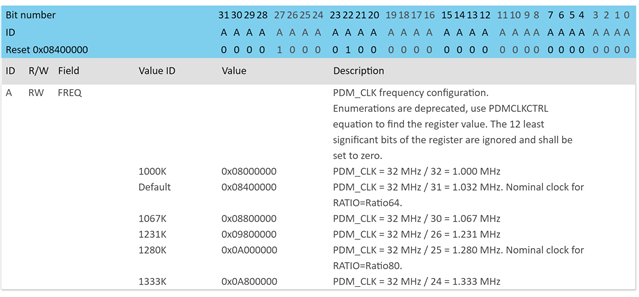

So that was two combinations 1) 64 RATIO + 1.024 M (or 1.033 M if using PCLK). Then for nRF53 came the addition of the ACLK, and the FREQ or 2) RATIO 80 + 1.280 M FREQ configuration.

So that was two combinations 1) 64 RATIO + 1.024 M (or 1.033 M if using PCLK). Then for nRF53 came the addition of the ACLK, and the FREQ or 2) RATIO 80 + 1.280 M FREQ configuration.