Hi,

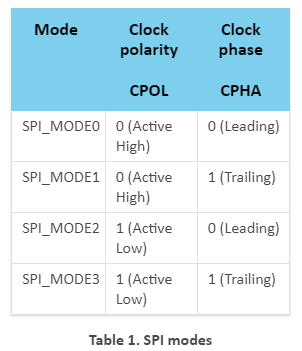

I am trying to interface nrf52840 with Arducam mini OV2640 2mp. I am trying to implement SPIM to communicate with the arducam. In the arducam OV2640 datasheet, to enable SPI communication, it is mentioned that "The ArduCAM SPI slave interface is fixed SPI mode 0 with POL = 0 and PHA = 1". In the nRF52840 product specification, different modes are mentioned for configuration as shown in the image below. I am confused which mode of nrf52840 should I select such that it corresponds to Arducam SPI mode POL=0 and PHA=1.