Hello,

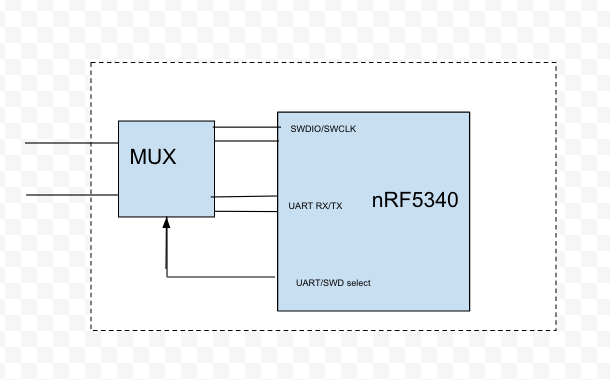

I am working on a custom board which has a multiplexer connected to route two output pins to either UART RX/TX lines or SWDIO/SWCLK.

The multiplexer is controlled by the nRF application, and selecting either mode works as expected (can enable UART comms and send messages at 1MBaud, or communicate over SWD when this mode is selected and attach a debugger and program).

I noticed an issue, however, that connecting a UART device externally while routed to the SWDIO/SWCLK pins on the nRF can cause the processor to halt, and I would like to understand what is happening. Specifically, I was able to isolate the issue down to the following error case, and was able to reproduce.

1. If SWCLK is driven high (1.8V)

2. And then SWDIO is temporarily driven low (short to ground briefly, or falling edge on SWDIO)

The processor halts, and does not resume operation, until drive on SWCLK is removed (internal pull-down on nRF5340 brings SWDIO low again).

On our custom board, during startup, if the UART lines are connected via the mux, an external pull-on UART RX causes SWCLK to pull high, and then a falling edge on UART TX (data transmission over the UART interface) causes the device to halt until the uart pull up is disconnected.

Can you please help me understand why this is happening? I think that the problem can be resolved by removing the pull up on UART RX (this is not ideal from our application because then that UART line is in a non-deterministic state and can lead to framing errors when the device is not connected, but this is better than having the nRF5340 stop responding.

Mostly I want to understand the failure mode to make sure that my solution works in all cases.

Thanks in advance!